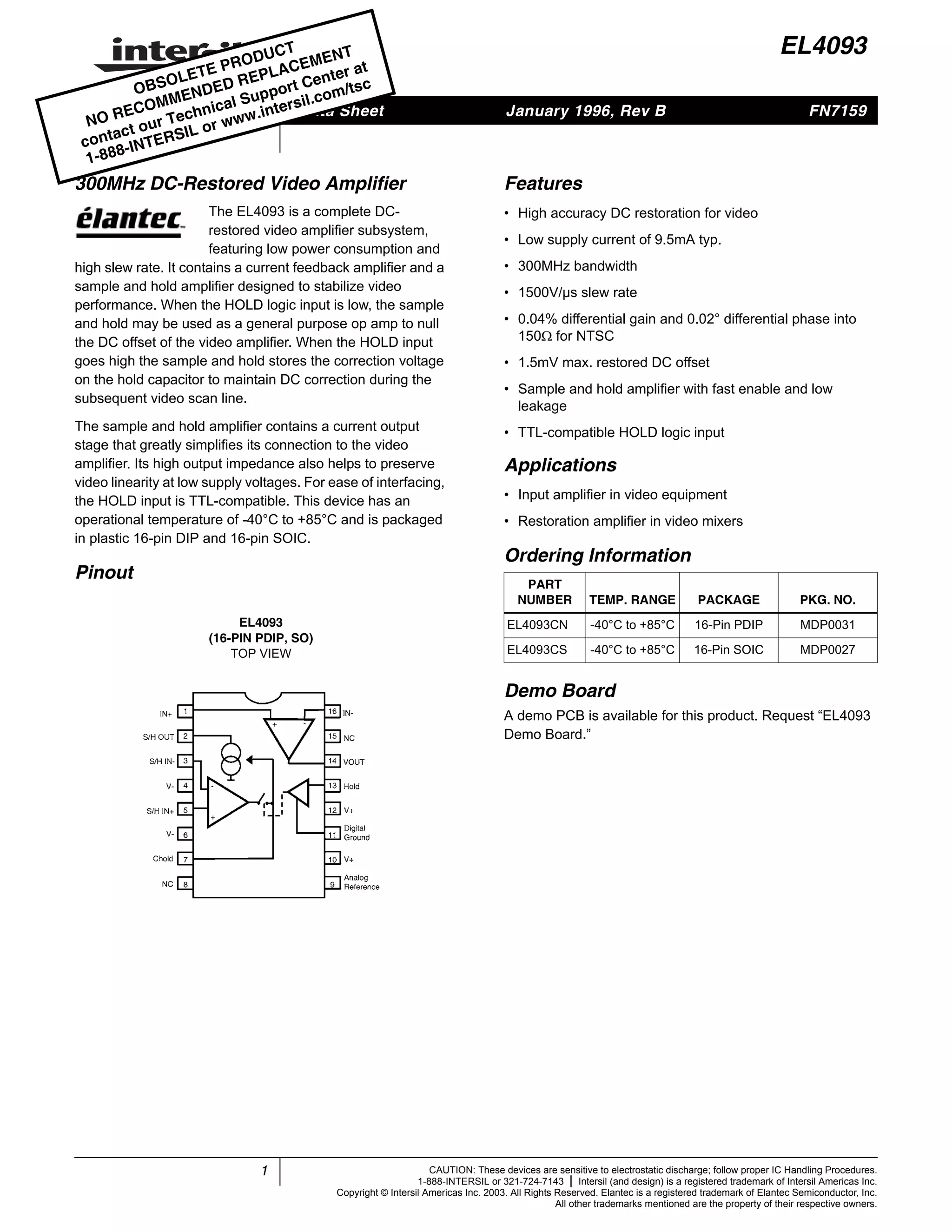

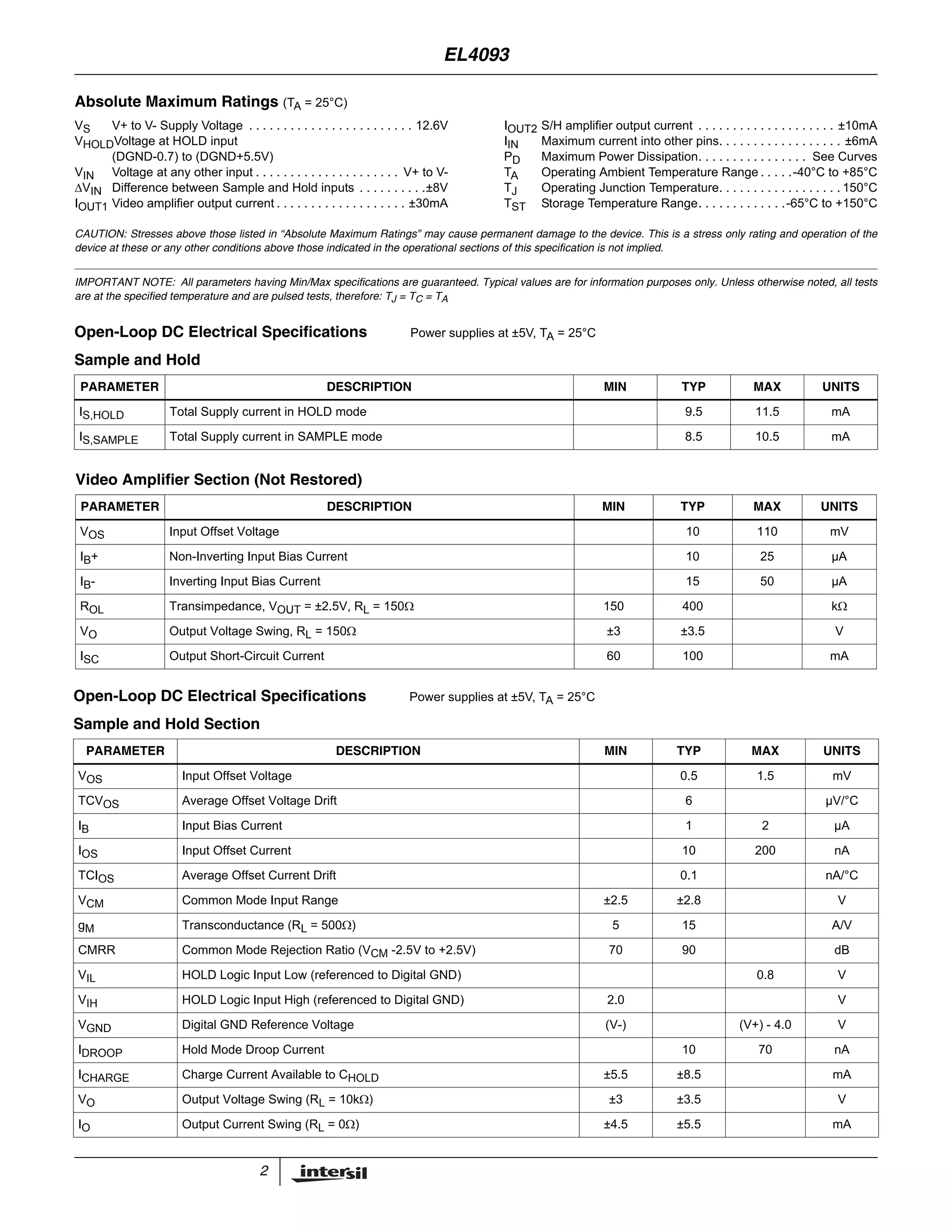

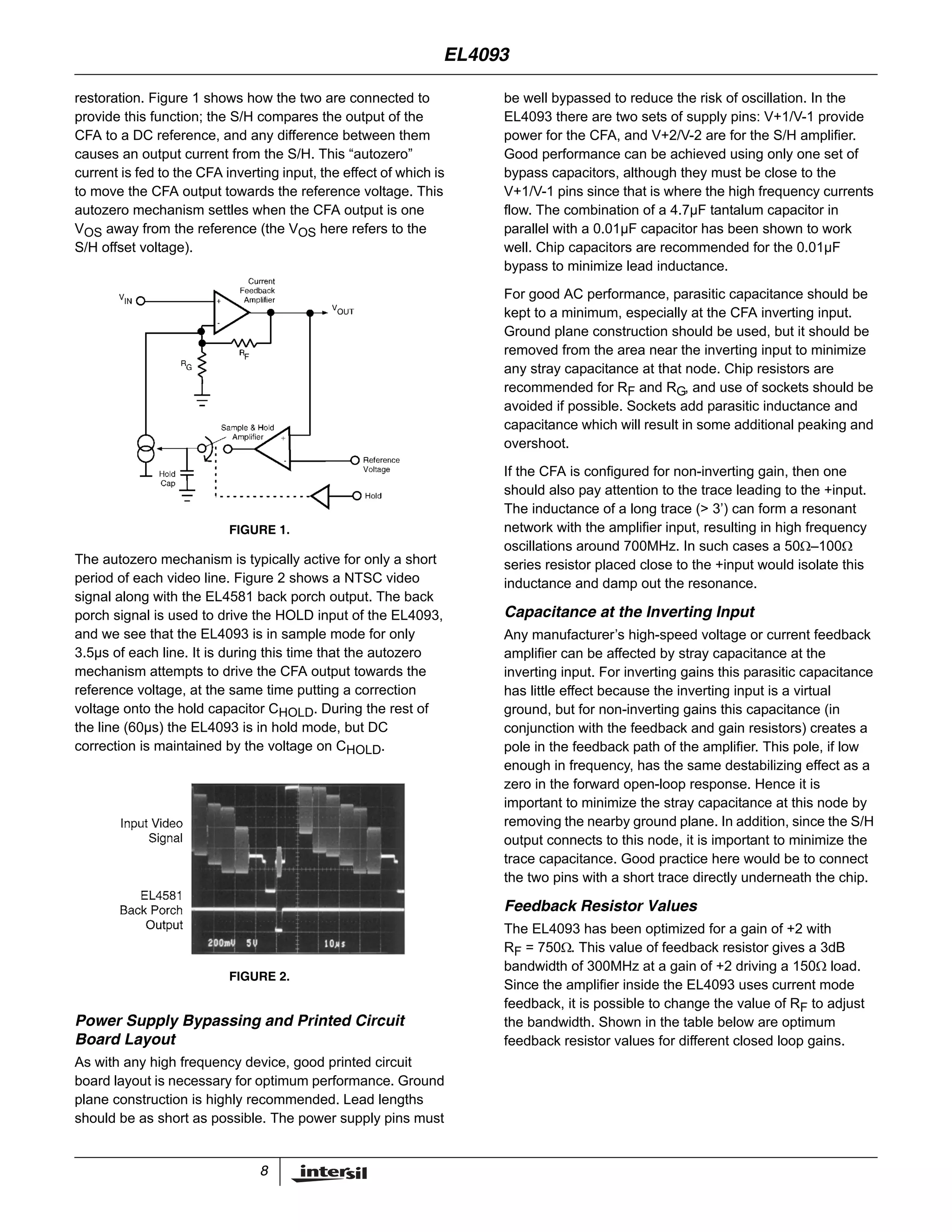

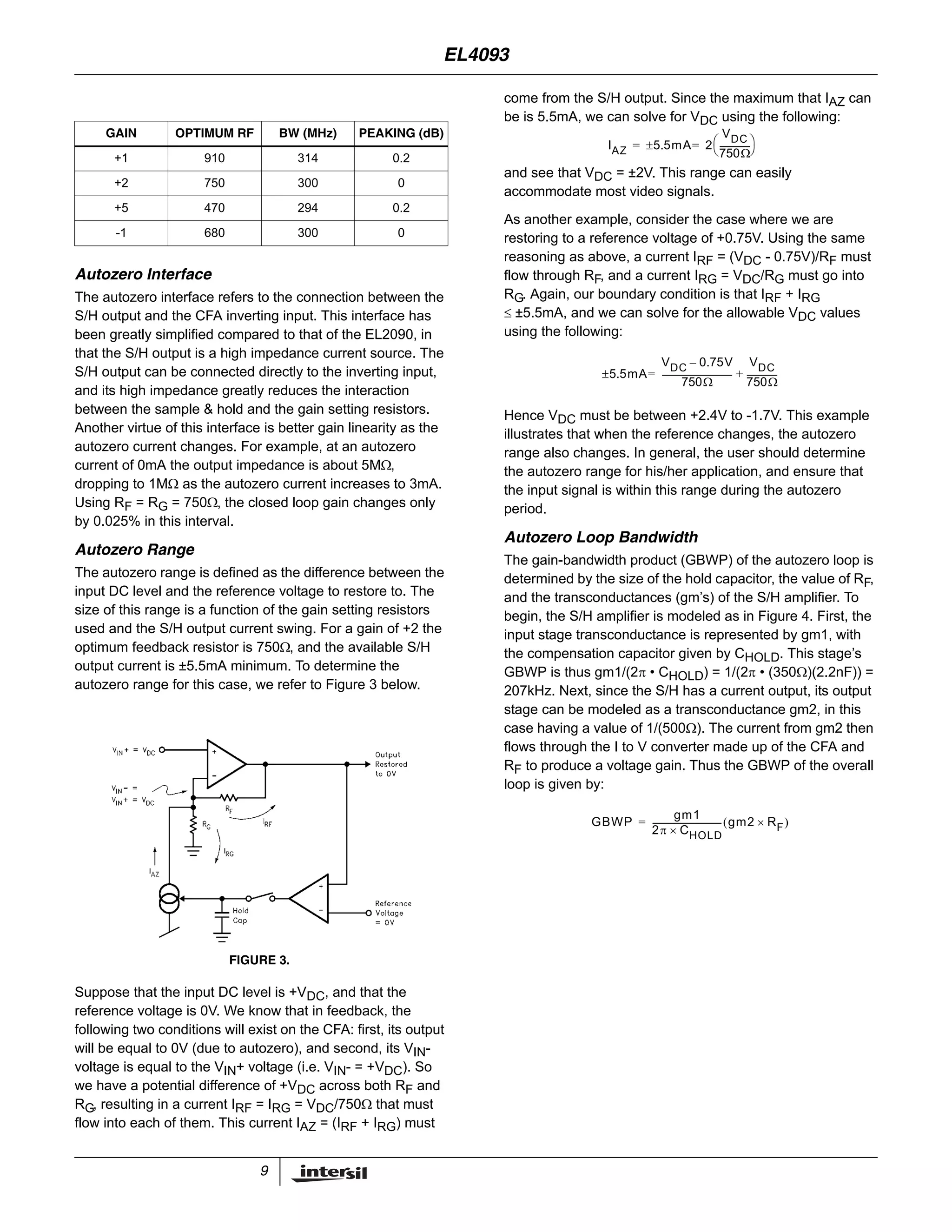

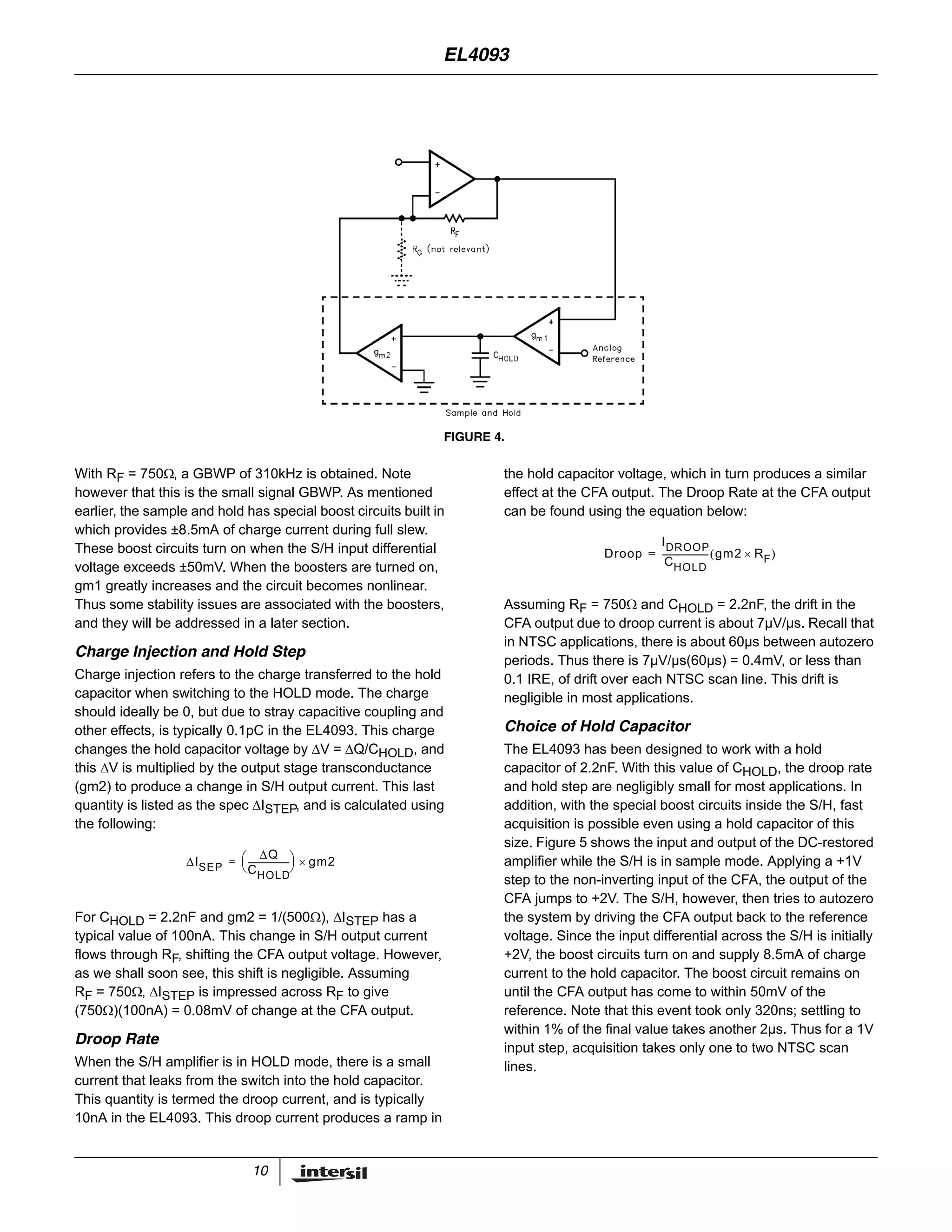

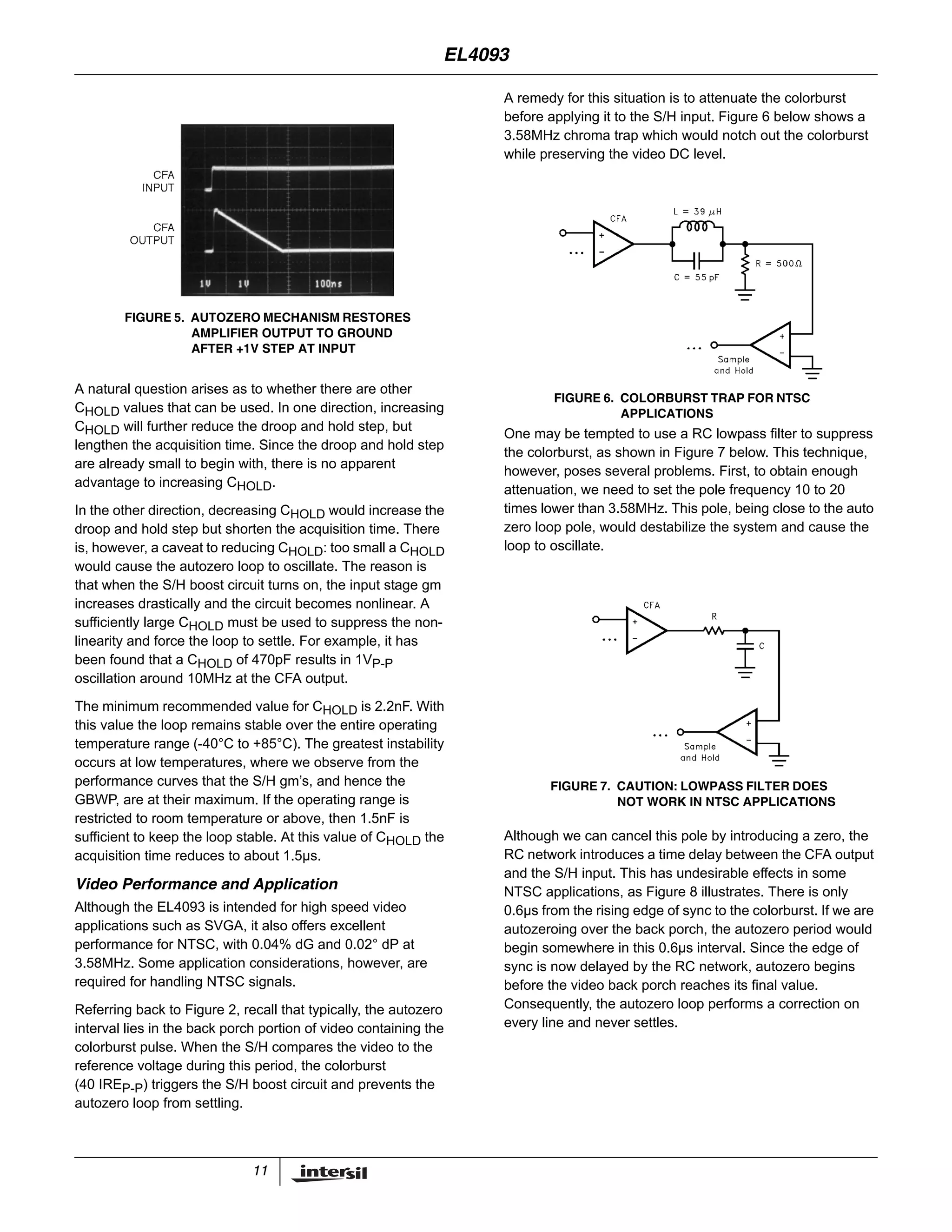

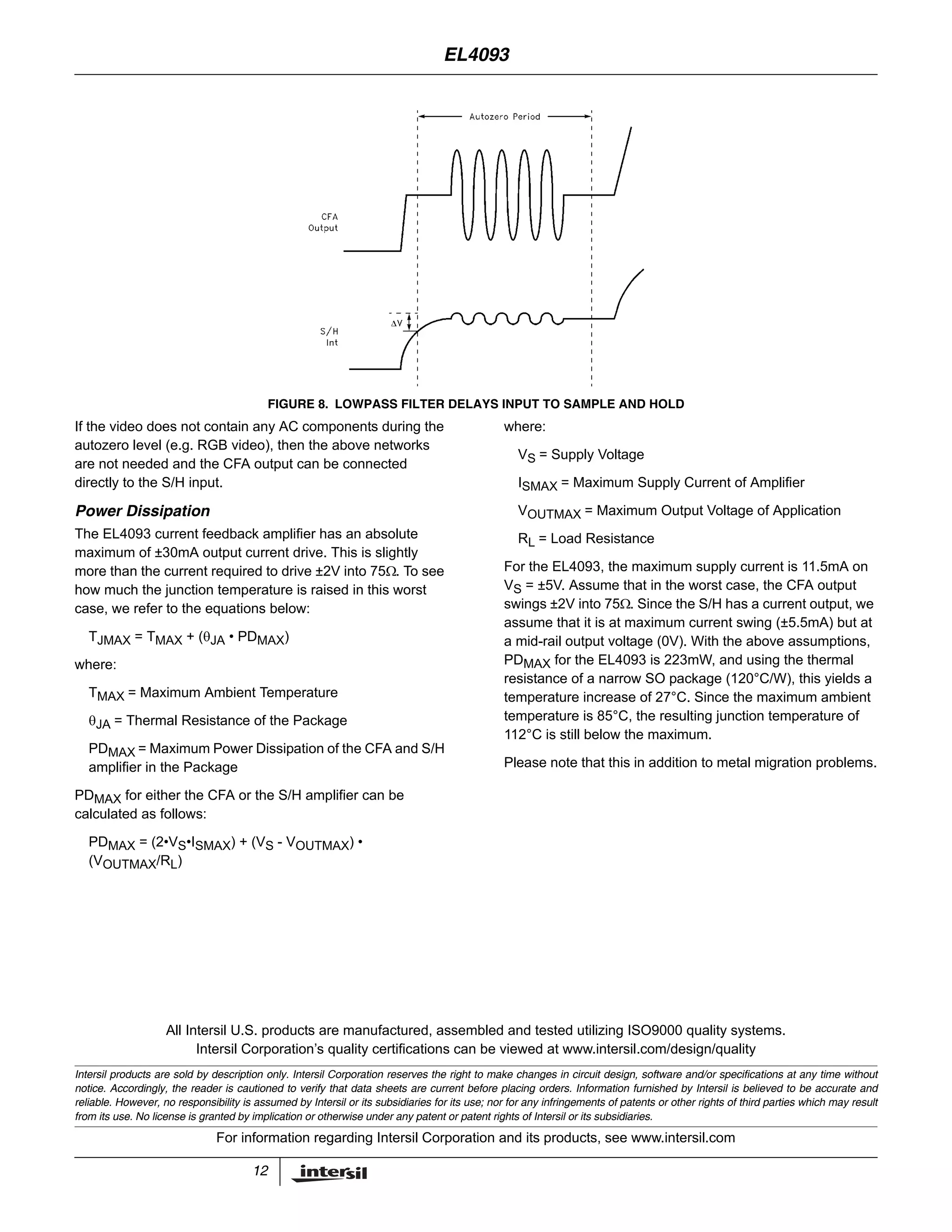

The document describes the EL4093, a 300MHz DC-restored video amplifier subsystem. It contains a current feedback amplifier (CFA) and sample and hold amplifier designed to stabilize video performance. When the HOLD input is low, the sample and hold can be used as a general purpose op amp. When HOLD goes high, the sample and hold stores a correction voltage to maintain DC correction during the subsequent video scan line. The device has applications in video equipment and restoration amplifiers, with features including high bandwidth, low power consumption, and TTL-compatible inputs. It is packaged in 16-pin DIP and SOIC packages.