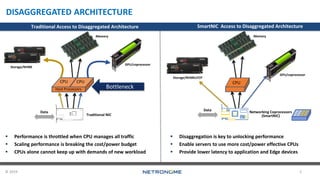

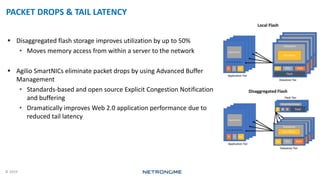

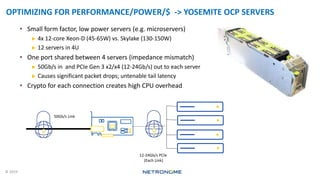

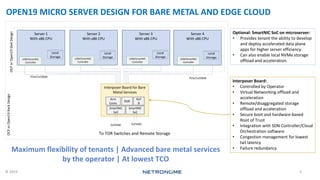

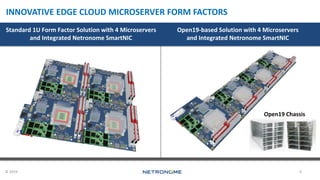

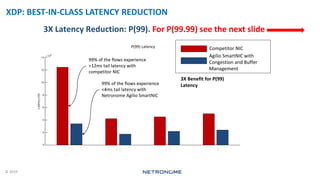

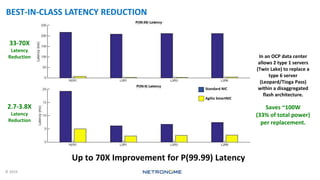

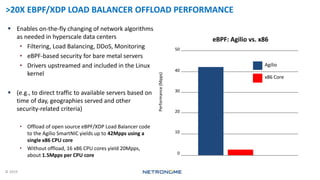

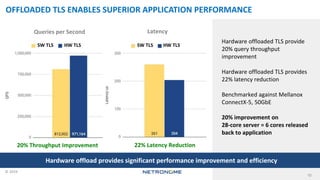

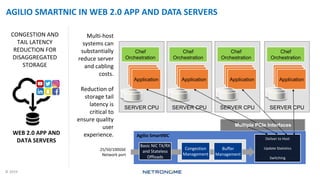

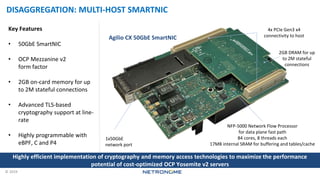

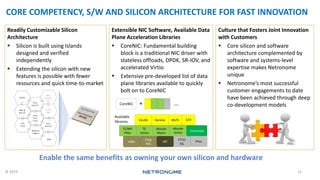

The document outlines the importance of disaggregated architecture in improving data center performance by optimizing CPU and network interactions, particularly for edge cloud applications. It emphasizes the role of smartNICs in reducing latency and enhancing throughput through advanced congestion management and hardware offloads. By leveraging innovative microserver designs and efficient resource allocation, the aim is to achieve significant power savings and performance improvements in cloud environments.