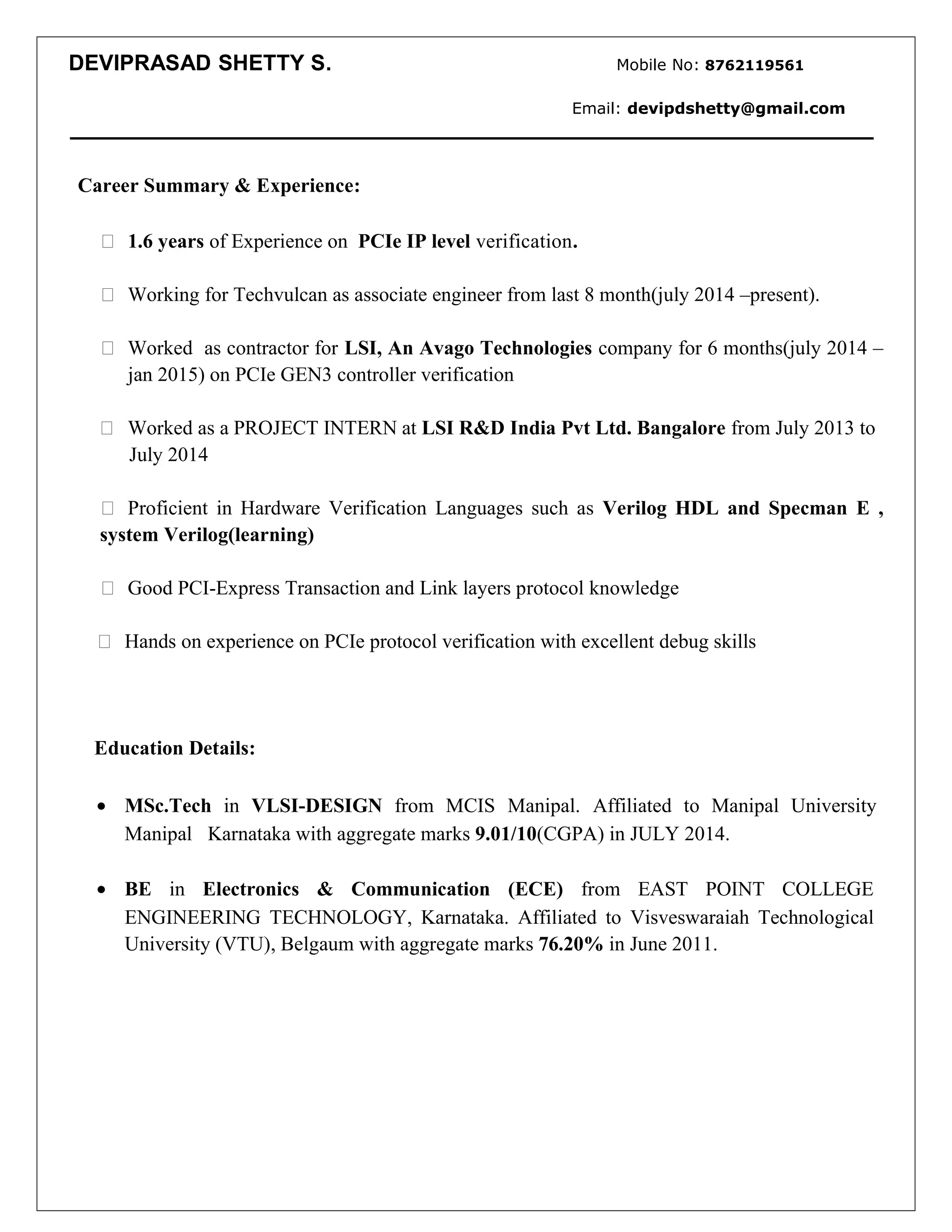

Deviprasad Shetty has over 1.6 years of experience in PCIe IP level verification. He has worked as a contractor for LSI and as a project intern at LSI R&D India. He is proficient in Verilog HDL, Specman E, and has knowledge of PCIe protocols. His education includes an MSc.Tech in VLSI Design from MCIS Manipal and a BE in Electronics and Communication. His projects include PCIe controller verification using Specman and asynchronous FIFO design and verification.