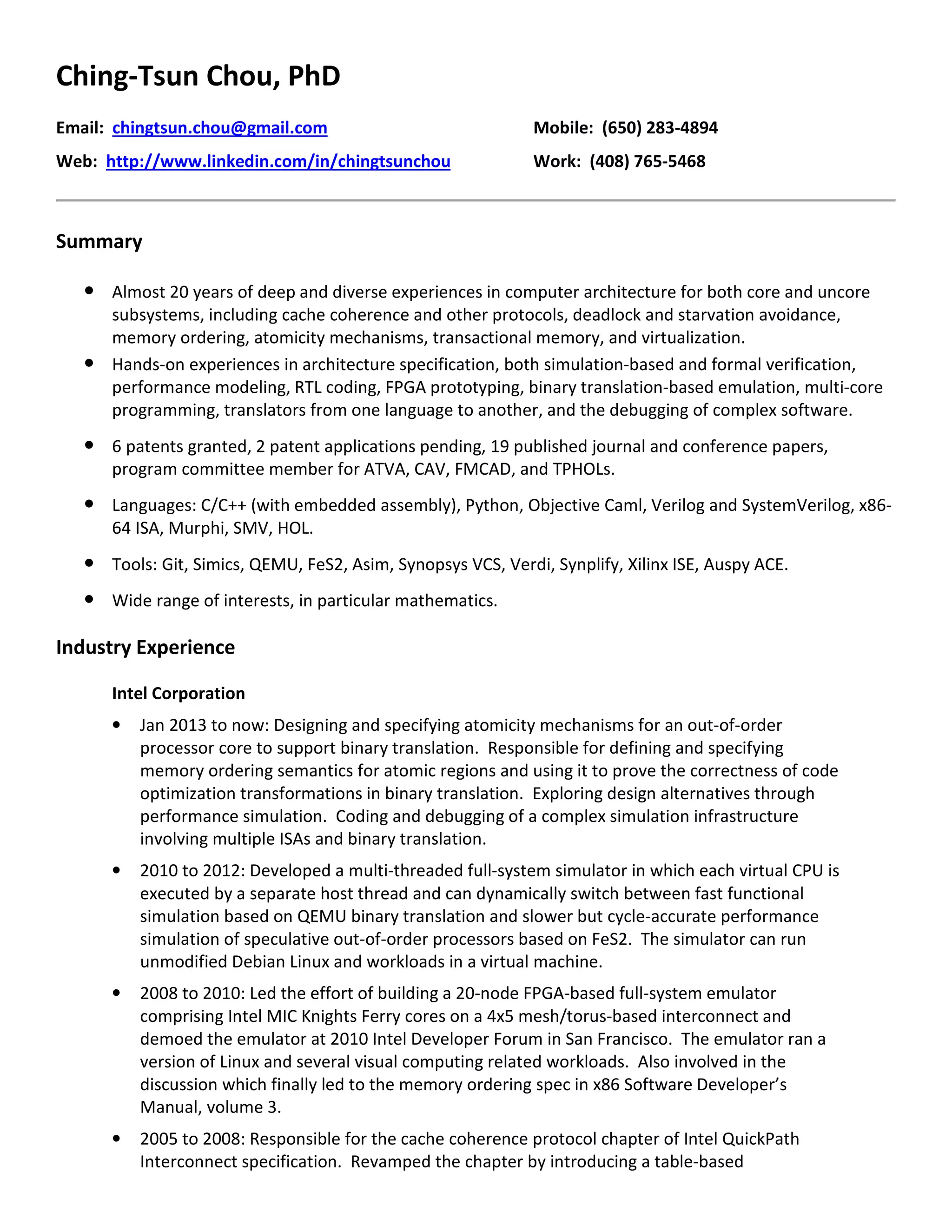

Ching-Tsun Chou has nearly 20 years of experience in computer architecture, including expertise in cache coherence protocols, memory ordering, atomicity mechanisms, and virtualization. He has worked at Intel since 2013 designing atomicity mechanisms for out-of-order processors and specifying memory ordering semantics. Prior to Intel, he led the development of an FPGA-based full-system emulator at Intel and designed synchronous circuits at Fujitsu Labs of America. He has 6 granted patents, 2 pending applications, and 19 publications in the field of computer architecture.