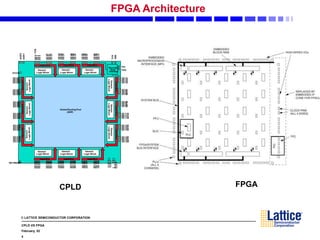

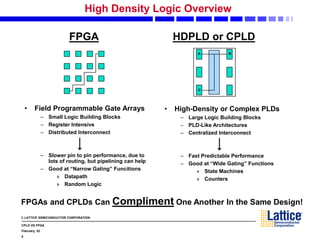

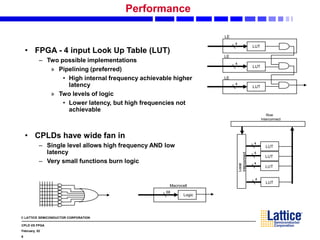

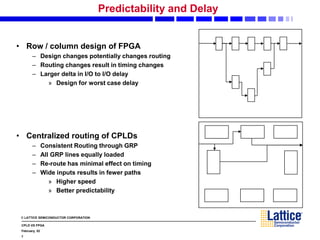

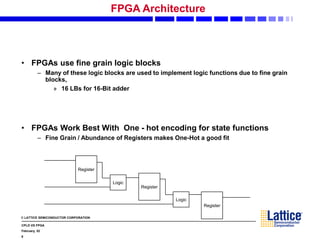

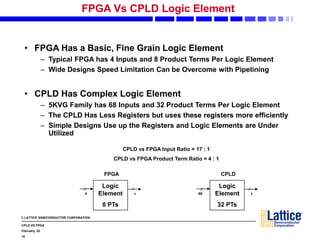

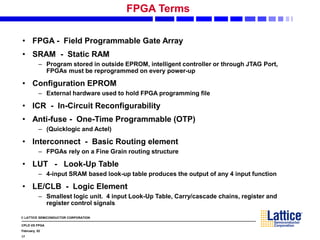

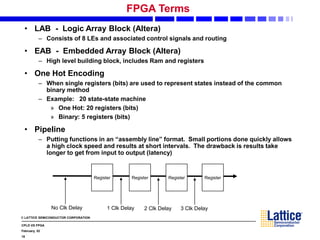

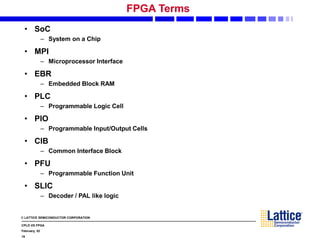

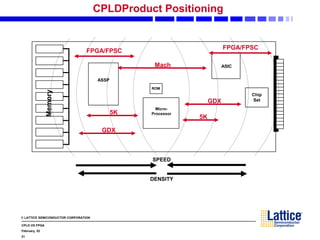

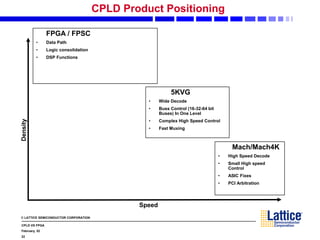

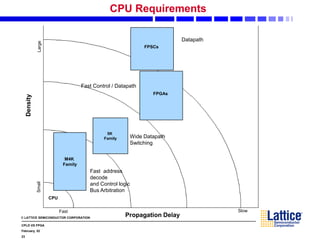

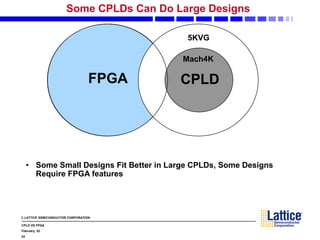

This document compares CPLDs and FPGAs, describing their architectures and use cases. CPLDs have coarse-grained architectures best for wide, fast functions and relatively small designs, while FPGAs have fine-grained architectures best for narrow, pipelined functions and large designs. CPLDs are better for applications needing high speed and predictability like state machines and counters, while FPGAs are better for large, register-intensive logic applications. The document provides positioning guidance, noting CPLDs are best for wide designs, speed-critical applications, and designs that are relatively small, while FPGAs are best for large, register-intensive designs and narrow, pipelinable functions.