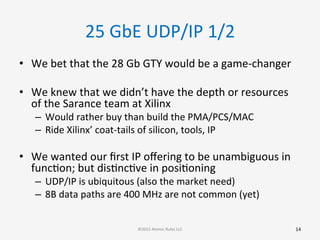

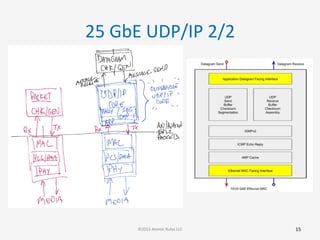

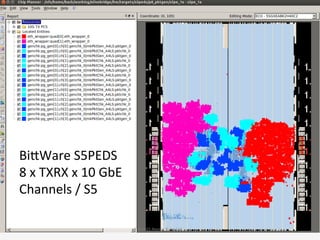

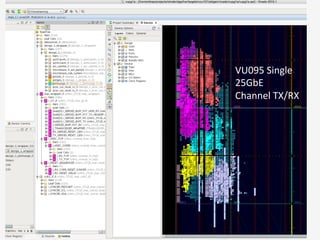

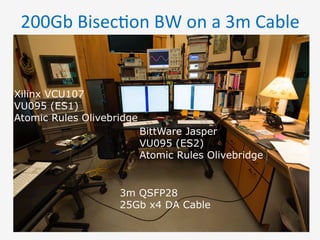

This document discusses tackling 400 MHz timing closure for 25/50/100 GbE designs. It describes conversations where an expert said timing closure shouldn't be an issue at 400 MHz with the Virtex UltraScale fabric. The author then attempted this but encountered difficulties meeting timing targets. The document explores architectural choices that impact timing closure and avoiding negative slack. It focuses on a 25 GbE UDP/IP design and strategies for achieving 400 MHz operation on a 20 nm FPGA.