This document discusses conditional processing, Boolean, and comparison instructions in CPUs. It covers the following topics:

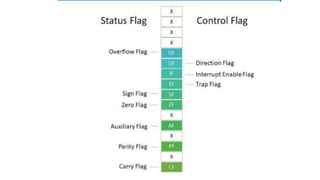

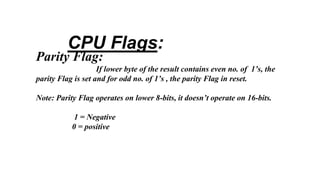

- The CPU flags register which contains status flags like carry, overflow, zero, and sign flags.

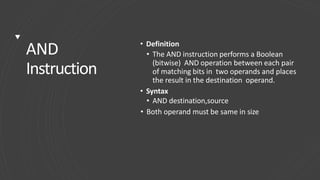

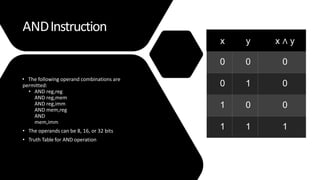

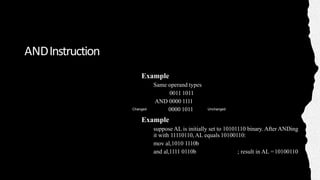

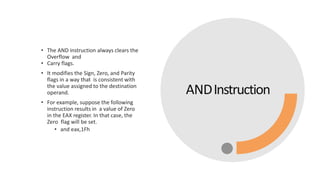

- The AND instruction which performs a bitwise AND operation and can be used to convert characters between lowercase and uppercase. It clears the overflow and carry flags.

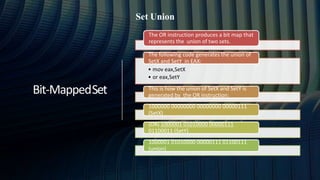

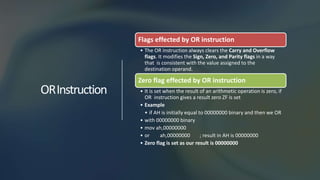

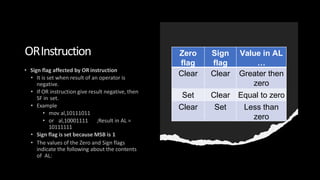

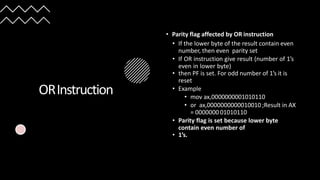

- The OR instruction which performs a bitwise OR operation and can be used to set bits. It clears the carry and overflow flags.

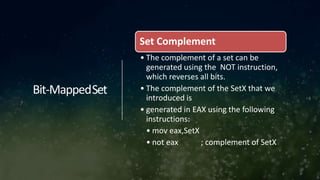

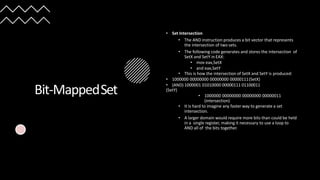

- How bitmaps can represent sets and how AND, OR, and NOT instructions can perform set operations like intersection, union, and complement on bitmaps.

![Bit-MappedSet

For example, the following

binary number uses bit

positions numbered from 0 on

the right to 31 on the left to

indicate that array elements 0,

1, 2, and 31 are members of

the set named SetX:

SetX = 10000000

00000000

00000000

00000111

We can easily check for set

membership by ANDing a

particular member’s bit

position

mov eax,SetX

and eax,10000b ;

is element[16] a

member of SetX?

If the AND instruction in this example clears the

Zero flag, we know that element [16] is a

member of SetX](https://image.slidesharecdn.com/conditionalprocessingbooleanandcomparisoninstructions-converted-230223183047-0a4e98f7/85/Conditional-Processing-Boolean-and-Comparison-Instructions-converted-pptx-28-320.jpg)