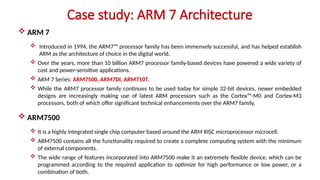

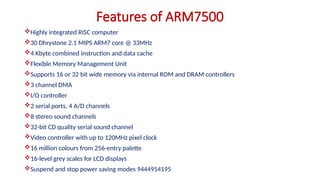

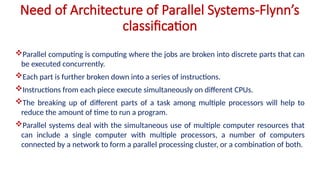

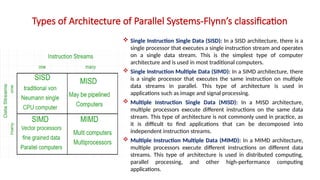

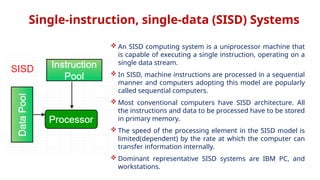

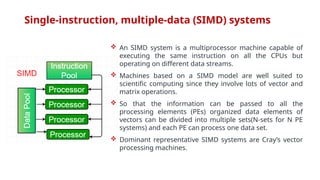

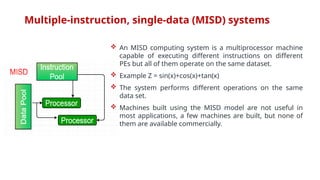

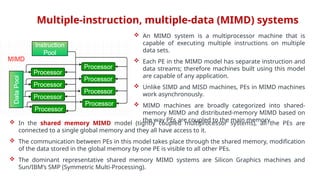

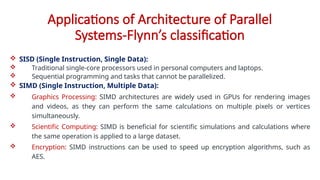

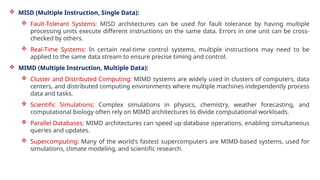

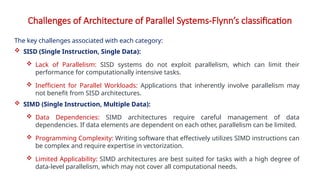

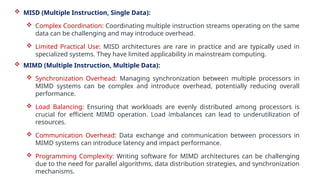

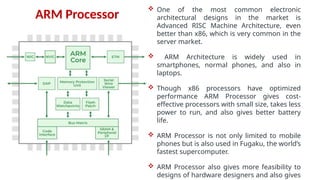

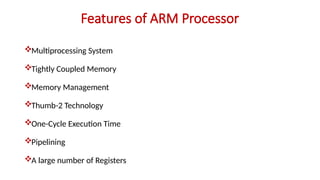

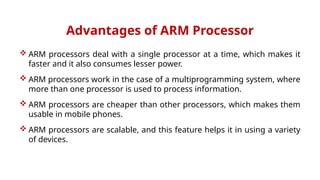

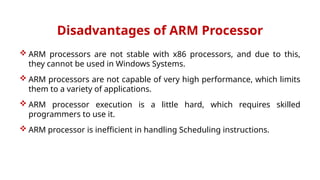

The document discusses the architecture of parallel systems, classified by Flynn's taxonomy, explaining various types like SISD, SIMD, MISD, and MIMD, along with their applications and challenges. It also details the ARM processor architecture, instruction sets such as Thumb, and highlights the advantages and disadvantages of ARM processors in various computing environments. Overall, the text emphasizes the significance of these architectures in optimizing performance and resource utilization in computing.

![ARM Processor: Memory load and Store instruction

ARM processors use load and store instructions to manipulate data stored in

memory.

These instructions are fundamental to the operation of ARM-based systems, and they

are used to move data between registers and memory.

In ARM assembly language, load and store instructions are typically represented as

"LDR" (Load Register) and "STR" (Store Register) instructions, respectively.

LDR (Load Register):

LDR Rd, [Rn, #offset]: Loads a word from memory at the address specified by Rn plus the #offset into

register Rd.

Example: LDR R0, [R1, #4] loads a word from the memory location at R1 + 4 into R0.](https://image.slidesharecdn.com/coau5pptfull-241117040739-0b8df2e0/85/Computer-organisation-and-architecture-unit-5-SRM-27-320.jpg)

![ STR (Store Register):

STR Rd, [Rn, #offset]: Stores the value in register Rd into memory at the address specified by

Rn plus the #offset.

Example: STR R0, [R1, #8] stores the value in R0 into the memory location at R1 + 8.

LDM (Load Multiple):

LDM Rn, {Rd1, Rd2, ...}: Loads multiple registers with values from memory starting at the

address in Rn. Useful for loading several values at once.

Example: LDM R1, {R2, R3, R4} loads values from memory into R2, R3, and R4 starting at the

address in R1.

STM (Store Multiple):

STM Rn, {Rd1, Rd2, ...}: Stores multiple registers' values into memory starting at the address

in Rn. Useful for saving several values at once.

Example: STM R1, {R2, R3, R4} stores the values in R2, R3, and R4 into memory starting at the

address in R1.](https://image.slidesharecdn.com/coau5pptfull-241117040739-0b8df2e0/85/Computer-organisation-and-architecture-unit-5-SRM-28-320.jpg)