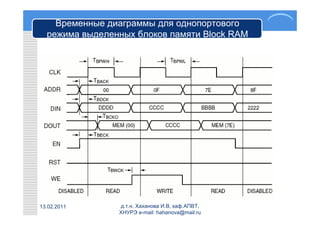

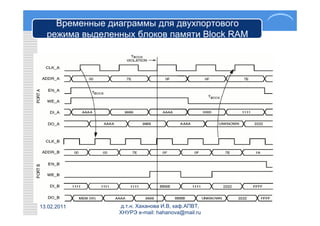

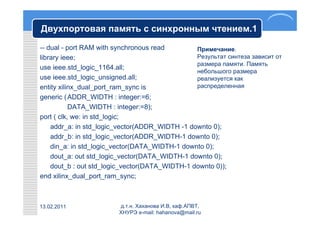

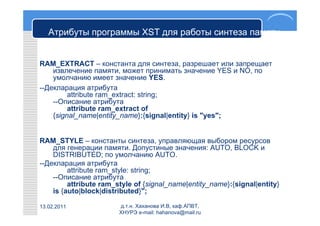

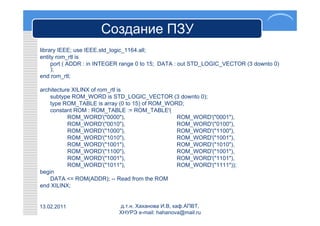

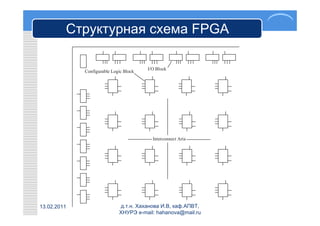

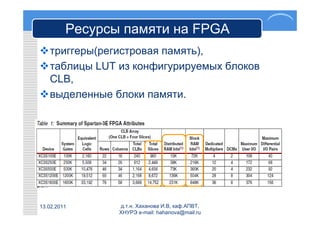

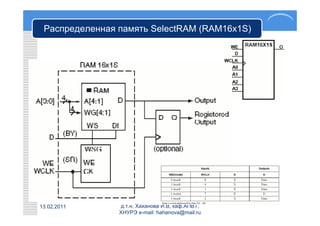

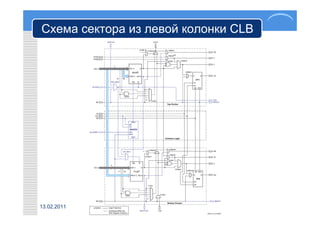

Документ посвящен проектированию памяти на FPGA и содержит лекцию, разработанную д.т.н. Хахановой И.В. Он охватывает различные аспекты, включая конфигурацию и использование триггеров, LUT таблиц и блоков RAM, а также модели памяти с синхронным и асинхронным чтением. Документ также содержит примеры реализаций памяти, временные диаграммы и атрибуты для синтеза памяти.

![Выделенные блоки памяти

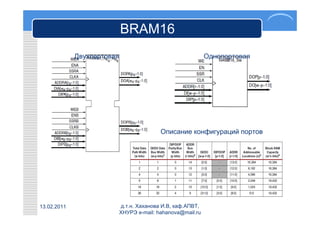

RAMB4_S#_S#

WEA

ENA

RSTA DOA[#:0]

CLKA

ADD[#:0]

DIA[#:0]

WEB

ENB

RSTB DOB[#:0]

CLKB

ADD[#:0]

DIB[#:0]

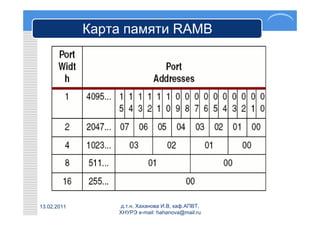

Width Depth ADDR Bus Data Bus

1 4096 A DDR<11:0> DATA<0>

2 2048 ADDR<10:0> DATA<1:0>

4 1024 A DDR<9:0> DATA<3:0>

8 512 A DDR<8:0> DATA<7:0>

16 256 A DDR<7:0> DATA<15:0>

13.02.2011 д.т.н. Хаханова И.В, каф.АПВТ,

ХНУРЭ e-mail: hahanova@mail.ru](https://image.slidesharecdn.com/2113-110221163410-phpapp02/85/2-11_3_-15-320.jpg)