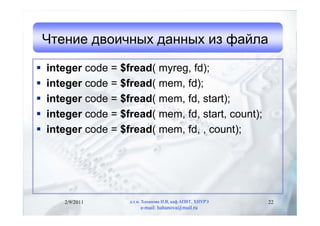

Документ представляет собой лекцию о принципах моделирования в Verilog на уровне вентильных и dataflow. Он охватывает стандартные логические элементы, синтаксис операторов присвоения, работу с задержками и примеры использования арифметических и логических операторов. Дополнительно обсуждаются системные задачи, функции работы с файлами и чтение двоичных данных.

![Оператор непрерывного назначения.1

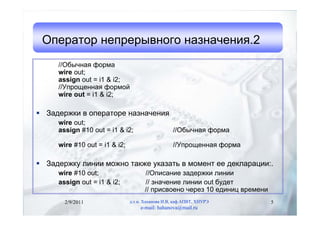

Синтаксис:

assign [drive_strength] [delay] net_value =

expression {,net_value = expression};

Примеры:

assign out=i1&i2;

assign addr[15:0]=addr1[15:0]^addr2[15:0];

assign {c_out, sum[3:0]}=a[3:0]+b[3:0]+c_in;

2/9/2011 д.т.н. Хаханова И.В, каф.АПВТ, ХНУРЭ 4

e-mail: hahanova@mail.ru](https://image.slidesharecdn.com/201103verilog-110209162015-phpapp02/85/2011-03_verilog-4-320.jpg)

![Операторы логические, отношения и равенства

Логические операторы

A=3; B=0;

A&&B=0 A||B=1 !A=0 !B=1

A = 2'b0x; B = 2'b10; // Операнд с элементом x

A && B = x // эквивалентно (x && 1)

Операторы отношения

reg [3:0] a, b; a = 4’b1100; b = 4’b0110;

a < b // равняется логическому 0 a > 8 // равняется логической 1

a <= b // равняется логическому 0 a >= 10 // равняется логической 1

a < 4’b1zzz // результат равен x a < 4’b1x01 // результат равен x

Операторы равенства

reg [3:0] a, b; a = 4’b1100; b = 4’b101x;

a == 4’b1100 // истина – логическая 1 a != 4’b1100 // ложь – логический 0

b == 4’b101x // результат равен x b != 4’b101x // результат равен x

b === 4’b101x // истина – логическая 1 b !== 4’b101x // ложь – логический 0

2/9/2011 д.т.н. Хаханова И.В, каф.АПВТ, ХНУРЭ 9

e-mail: hahanova@mail.ru](https://image.slidesharecdn.com/201103verilog-110209162015-phpapp02/85/2011-03_verilog-9-320.jpg)

![Побитовые операторы

~^

& 0 1 x z ^ 0 1 x z | 0 1 x z 0 1 x z ~ 0 1 x z

^~

0 0 0 0 0 0 0 1 x x 0 0 1 x x 0 1 0 x x 1 0 X X

1 0 1 x x 1 1 0 x x 1 1 1 1 1 1 0 1 x x

x 0 x x x x x x x x x x 1 x x x x x x x

z 0 x x x z x x x x z x 1 x x z x x x x

reg [7:0] a, b; a = 8’b1010xzxz; b = 8’b10010011;

a&b // поразрядное И, результат 8’b100000xx;

a|b // поразрядное ИЛИ, результат 8’b1011xx11;

a^b // поразрядное по модулю 2, результат 8’b0011xxxx;

a ~^ b // поразрядное по модулю 2 с инверсией выхода,

// результат 8’b1100xxxx;

~a // поразрядная инверсия, результат 8’b0101xxxx;

2/9/2011 д.т.н. Хаханова И.В, каф.АПВТ, ХНУРЭ 10

e-mail: hahanova@mail.ru](https://image.slidesharecdn.com/201103verilog-110209162015-phpapp02/85/2011-03_verilog-10-320.jpg)

![Операторы сдвига

Операторы сдвига Операторы сдвига

//x=4'b1100 Оператор Описание

y=x>>1 //y=4'b0110 a << b Сдвиг влево

y=x<<1 // y=4'b1000 a >> b Сдвиг вправо

y=x<<2 //y=4'b0000 a <<< b Знаковый сдвиг влево

a >>> b Знаковый сдвиг вправо

reg [3:0] a; a = 4’b1111;

a << 3 = 4’b1000 a >> 3 = 4’b0001

a << 1’bz = 4’bxxxx a >> 1’bx = 4’bxxxx

reg [7:0] r8;

r8 = a >>> b; // Сдвиг a вправо на b разрядов,

// старшие биты заполняются значением a[7]

2/9/2011 д.т.н. Хаханова И.В, каф.АПВТ, ХНУРЭ 12

e-mail: hahanova@mail.ru](https://image.slidesharecdn.com/201103verilog-110209162015-phpapp02/85/2011-03_verilog-12-320.jpg)

![Системные задачи и функции.3

$stop [(n)];

$finish [(n)];

Режимы диагностических сообщений задач $stop и $finish

n Сообщ ение

0 Отсутствует

1 Время моделирования

Время моделированияи и работы CPU,

2

размер используемой памяти

2/9/2011 д.т.н. Хаханова И.В, каф.АПВТ, ХНУРЭ 18

e-mail: hahanova@mail.ru](https://image.slidesharecdn.com/201103verilog-110209162015-phpapp02/85/2011-03_verilog-18-320.jpg)

![Системные задачи и функции.4

$printtimescale [ ( hierarchical_name ) ] ;

Пример:

// функции

`timescale 1 ms / 1 us

integer $time module a_dat;

integer $stime initial

real $realtime $printtimescale;

endmodule

Задача $printtimescale – выводит единицы измерения и

точность вычисления времени для указанного модуля

hierarchical_name. Системные функции $time и $stime

возвращают текущее время моделирования в виде 64- и 32-

битового целого числа, а функция $realtime – в вещественном

формате.

2/9/2011 д.т.н. Хаханова И.В, каф.АПВТ, ХНУРЭ 19

e-mail: hahanova@mail.ru](https://image.slidesharecdn.com/201103verilog-110209162015-phpapp02/85/2011-03_verilog-19-320.jpg)

![Загрузка памяти из файла

$readmemb ( " file_name " , memory_name [ ,

start_addr [ , finish_addr ] ] ) ;

| $readmemh ( " file_name " , memory_name [ ,

start_addr [ , finish_addr ] ] ) ;

Примеры

reg [7:0] mem[1:256];

initial $readmemh("mem.data", mem);

initial $readmemh("mem.data", mem, 16);

initial $readmemh("mem.data", mem, 128, 1);

2/9/2011 д.т.н. Хаханова И.В, каф.АПВТ, ХНУРЭ 23

e-mail: hahanova@mail.ru](https://image.slidesharecdn.com/201103verilog-110209162015-phpapp02/85/2011-03_verilog-23-320.jpg)

![$random()

Размер возвращаемых значенй соответствует

типу integer.

Пример использования функции $random.

parameter SEED = 33;

reg [31:0] vector;

always @(posedge clock)

vector = $random (SEED);

2/9/2011 д.т.н. Хаханова И.В, каф.АПВТ, ХНУРЭ 24

e-mail: hahanova@mail.ru](https://image.slidesharecdn.com/201103verilog-110209162015-phpapp02/85/2011-03_verilog-24-320.jpg)