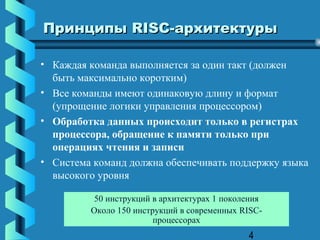

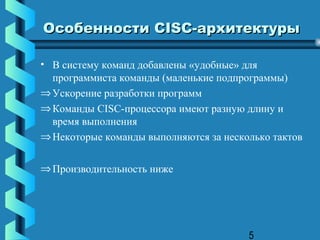

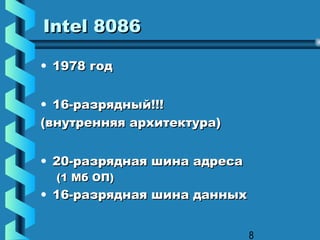

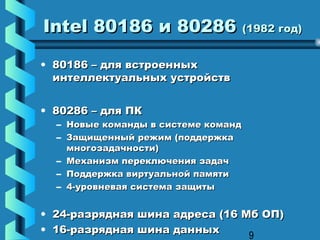

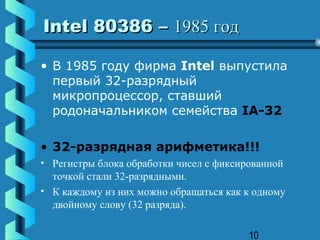

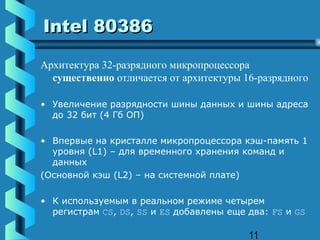

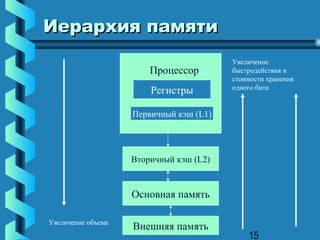

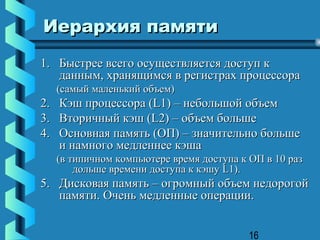

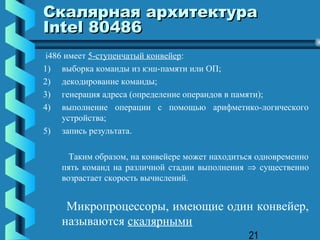

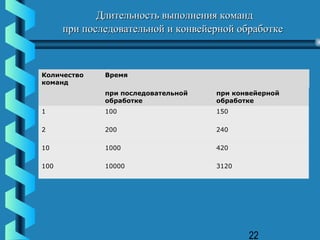

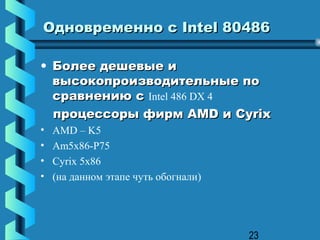

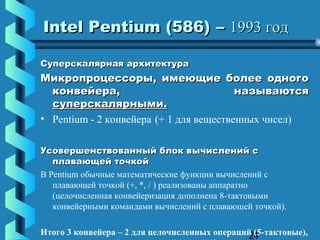

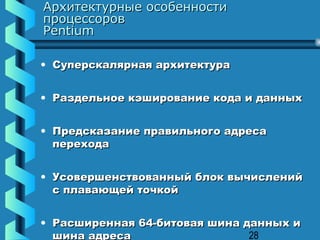

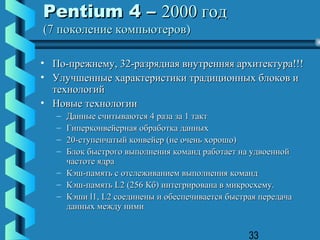

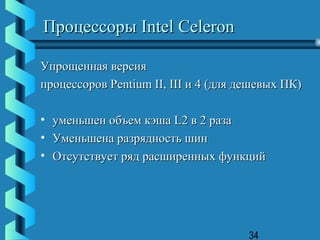

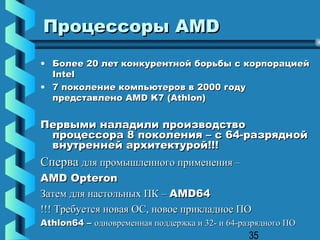

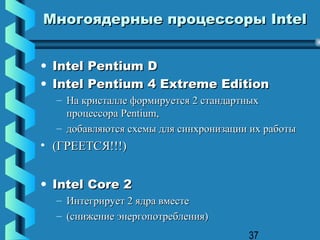

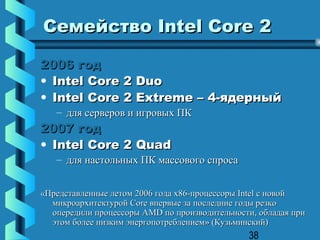

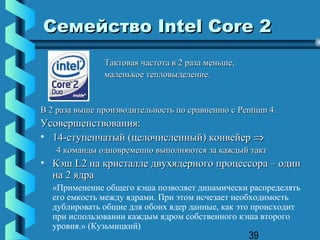

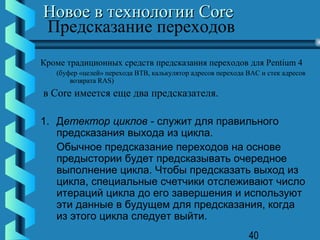

Документ представляет лекцию по архитектуре персональных компьютеров, рассматривая различия между архитектурами CISC и RISC, а также описание исторического развития процессоров от Intel, включая их модели и характеристики. В нем подробно обсуждаются принципы работы кэш-памяти и иерархии памяти, а также архитектурные особенности различных поколений процессоров, включая технологии, влияющие на производительность. Упоминаются ведущие производители процессоров, такие как Intel и AMD, и описаны многопоточные технологии, которые привели к разработке многоядерных процессоров.

![Двухъядерный процессор

Intel® Core™2 Extreme

• «Двухъядерные процессоры Intel Core 2 Extreme

обеспечивают энергосбережение и высокую

производительность в играх, а также потрясающее

качество видео и звука.» [www.intel.ru]

43](https://image.slidesharecdn.com/prezosobmikroproc-121130105136-phpapp02/85/Prez-osob-mikroproc-43-320.jpg)