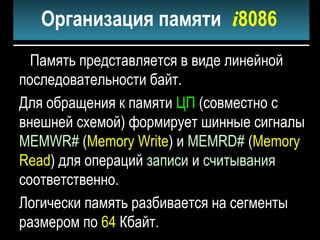

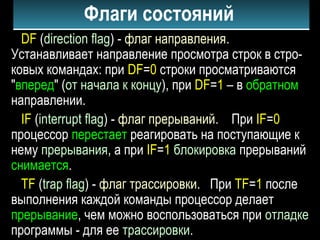

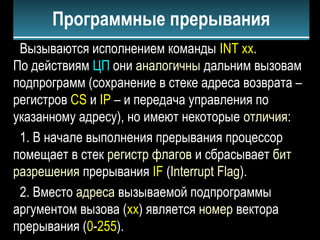

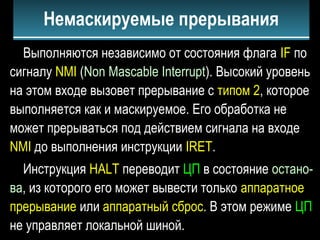

Документ описывает организацию и работу памяти процессора i8086, включая ее сегментацию, типы адресов и структуры регистров. Он также рассматривает различные типы прерываний, методы доступа к устройствам ввода-вывода и особенности представления данных в памяти. В документе подробно объясняются функции регистров, включая регистры общего назначения, сегментные регистры и регистр флагов.