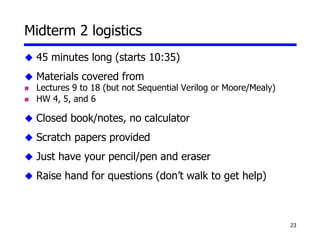

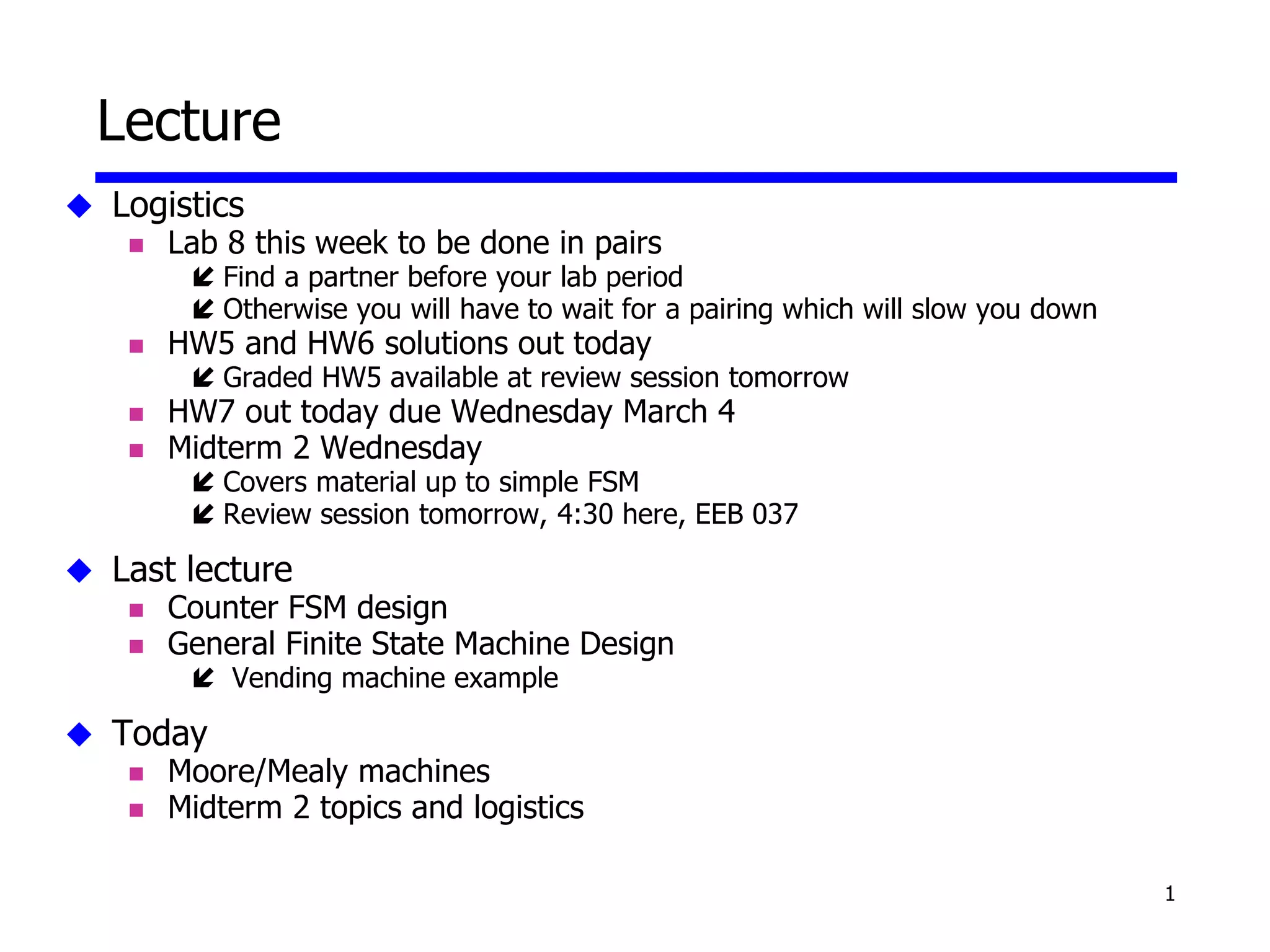

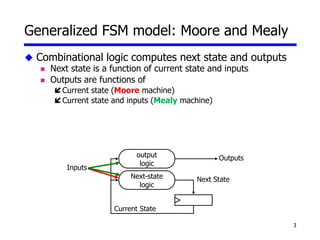

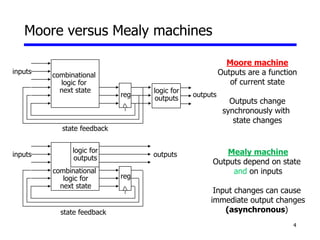

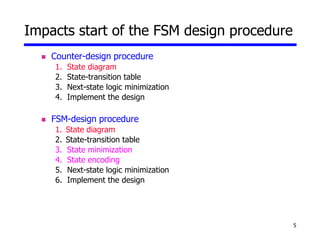

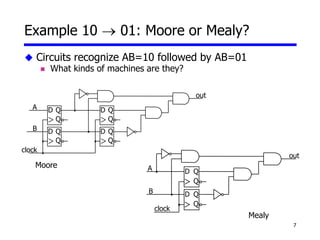

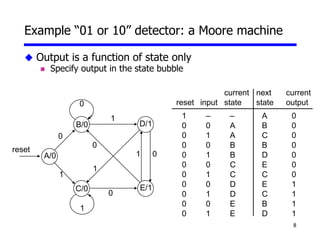

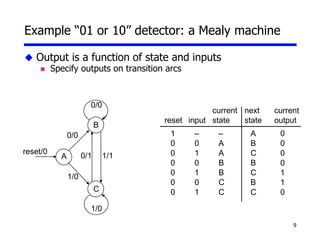

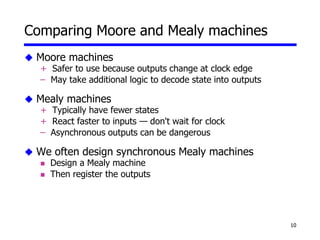

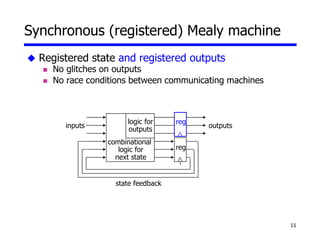

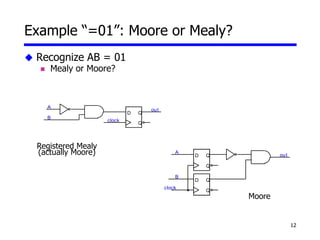

The document provides information about an upcoming lab, homework assignments, and midterm for a class. It discusses Moore and Mealy finite state machines and gives examples to illustrate the differences between them. Details are also given about the topics and format for the upcoming Midterm 2 exam.

![6

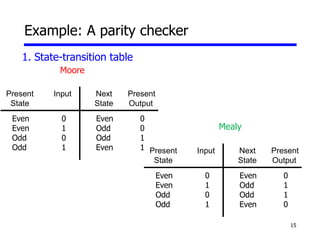

State Diagrams

Moore machine

Each state is labeled by a pair:

state-name/output or state-name [output]

Mealy machine

Each transition arc is labeled by a pair:

input-condition/output](https://image.slidesharecdn.com/19-mooremealy-221212150259-689608ef/85/19-MooreMealy-ppt-6-320.jpg)

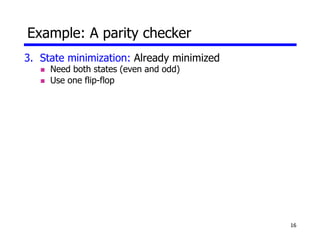

![14

Example: A parity checker

Even

[0]

Odd

[1]

0

1 1

1. State diagram

Moore Mealy

Even

[0]

Odd

[1]

0

1 1

0/0

1/1 1/0

0/1](https://image.slidesharecdn.com/19-mooremealy-221212150259-689608ef/85/19-MooreMealy-ppt-14-320.jpg)