NMOS PPT for 2nd year

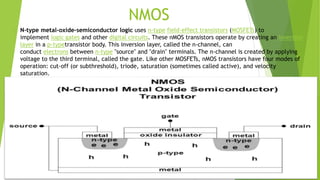

- 1. NMOS N-type metal-oxide-semiconductor logic uses n-type field-effect transistors (MOSFETs) to implement logic gates and other digital circuits. These nMOS transistors operate by creating an inversion layer in a p-typetransistor body. This inversion layer, called the n-channel, can conduct electrons between n-type "source" and "drain" terminals. The n-channel is created by applying voltage to the third terminal, called the gate. Like other MOSFETs, nMOS transistors have four modes of operation: cut-off (or subthreshold), triode, saturation (sometimes called active), and velocity saturation.

- 2. As an example, here is a NOR gate implemented in schematic NMOS. If either input A or input B is high (logic 1, = True), the respective MOS transistor acts as a very low resistance between the output and the negative supply, forcing the output to be low (logic 0, = False). When both A and B are high, both transistors are conductive, creating an even lower resistance path to ground. The only case where the output is high is when both transistors are off, which occurs only when both A and B are low, thus satisfying the truth table of a NOR gate. A B A NOR B 0 0 1 0 1 0 1 0 0 1 1 0

- 3. Additionally, just like in DTL, TTL, ECL, etc., the asymmetric input logic levels make NMOS and PMOS circuits more susceptible to noise than CMOS. These disadvantages are why the CMOS logic now has supplanted most of these types in most high-speed digital circuits such as microprocessors (despite the fact that CMOS was originally very slow compared to logic gates built with bipolar transistors).

- 4. ADVANTAGES OF NMOS 1. The number of diffusions steps required is the lowest. Hence, cost per gate is the lowest. 2. Very low power dissipation (on the order of a few nW). 3. Power supply can be varied from 5 V to 15 V possible. 4. Only NMOS transistors are used, no isolation-islands are required. Hence, highest packing density of all logic families. Suitable for VSLI, ULSI etc. DISADVANTAGES OF NMOS 1. MOS transistors are also capacitors. Hence, speed of operation is lowest due to very high capacitive loading. 2. Large propagation delay per gate. 3. Higher power dissipation than CMOS gates. 4. This technology has not acquired as much popularity as the CMOS technology. CMOS, because of its lower power dissipation and higher speed of operation has replaced NMOS almost completely.