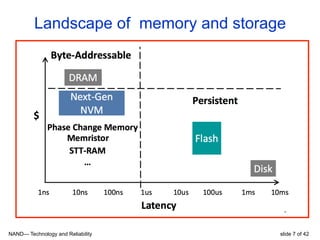

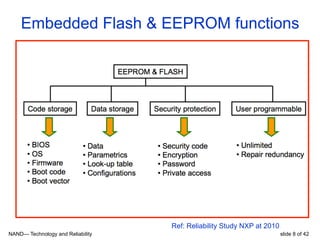

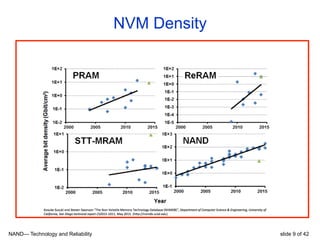

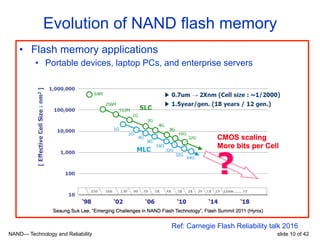

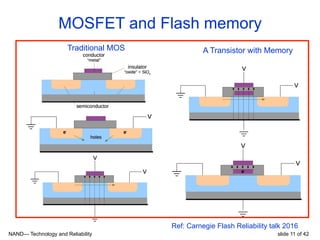

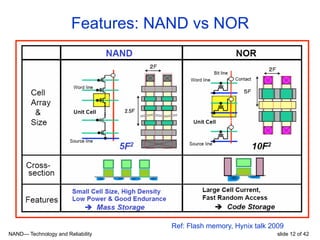

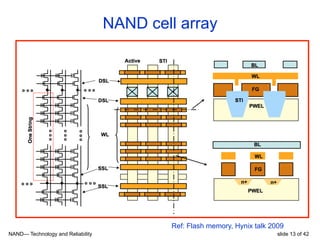

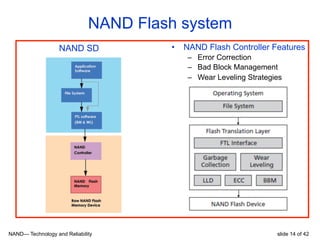

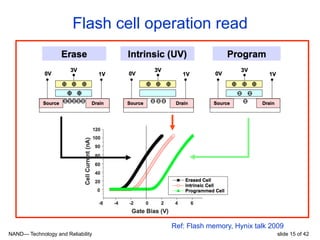

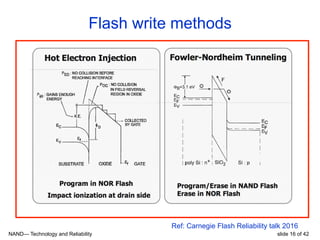

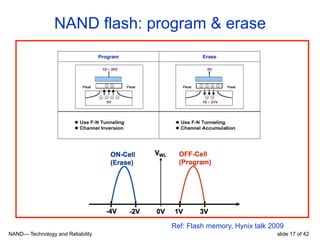

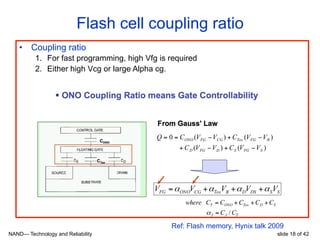

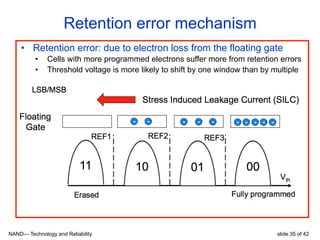

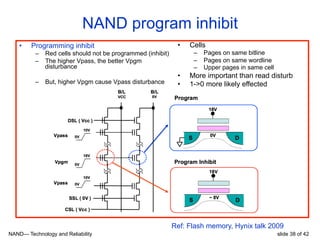

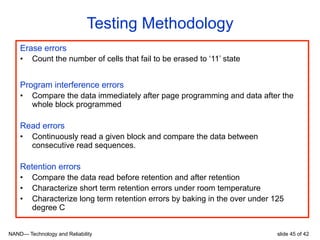

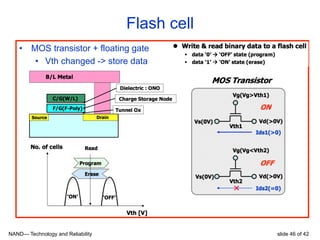

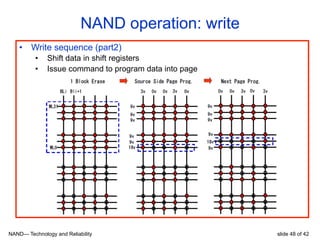

This document provides an overview of NAND flash memory technology and reliability issues. It begins with introductions to memory technologies and flash applications. The document then discusses NAND flash cell structure and operation, including programming, erasing, and reading. Key reliability issues covered include endurance, data retention, and program interference. The document provides references and outlines potential failure mechanisms and mitigation techniques like error correction codes and wear leveling.

![NAND— Technology and Reliability slide 3 of 42

References

[1] Chimenton et al., “Improving Performance and Reliability of NOR-Flash

arrays by using Pulsed Operation,” Microelectronics Reliability, Jul 2006.

[2] Micheloni et al., “Ch5. Error Correction Codes for Non-volatile Memories”,

Springer International publications, 2008.

[3] Hynix, “Flash Memory Technology”, Hynix Semiconductors Micron Tech Slides,

2009.

[4] Khiwan Choi, “NAND Flash Memory”, Samsung electronics Slides, 2010.

[5] Chimenton et al., “A Statistical Model of Erratic Behaviors in Flash Memory

Arrays,” IEEE Transactions on Electron devices, Nov 2011.

[6] Zambelli et al., “Nonvolatile Memory Partitioning Scheme for Technology-

Based Performance-Reliability Tradeoff,” IEEE Embedded Systems Letters,

March 2011.

[7] Meza et al., “A Large-Scale Study of Flash Memory Failures in the Field”,

SIGMETRICS, 2015.

[8] Onur Mutlu, “Reliability (and Security) Issues of DRAM and NAND Flash

Scaling”, Memory Reliability Workshop slides, Carnegie Mellon, 2016.

[9] Spinelli et al., “Reliability of NAND Flash Memories: Planar Cells and Emerging

Issues in 3D Devices”, IEEE Transactions on Computers, 2017.](https://image.slidesharecdn.com/01nandflashreliabilitynotes-180525231243/85/01-nand-flash_reliability_notes-3-320.jpg)