Mca2050 computer architecture

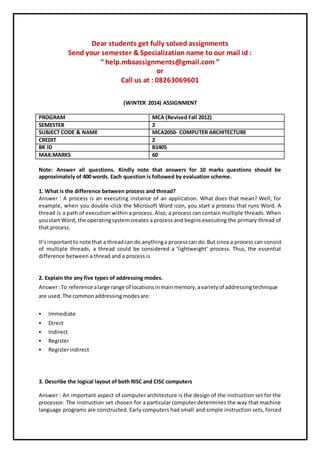

- 1. Dear students get fully solved assignments Send your semester & Specialization name to our mail id : “ help.mbaassignments@gmail.com ” or Call us at : 08263069601 (WINTER 2014) ASSIGNMENT PROGRAM MCA (Revised Fall 2012) SEMESTER 2 SUBJECT CODE & NAME MCA2050- COMPUTER ARCHITECTURE CREDIT 2 BK ID B1405 MAX.MARKS 60 Note: Answer all questions. Kindly note that answers for 10 marks questions should be approximately of 400 words. Each question is followed by evaluation scheme. 1. What is the difference between process and thread? Answer : A process is an executing instance of an application. What does that mean? Well, for example, when you double-click the Microsoft Word icon, you start a process that runs Word. A thread is a path of execution within a process. Also, a process can contain multiple threads. When youstart Word, the operatingsystemcreates a process and begins executing the primary thread of that process. It’simportantto note that a threadcan do anythinga processcan do.But since a process can consist of multiple threads, a thread could be considered a ‘lightweight’ process. Thus, the essential difference between a thread and a process is 2. Explain the any five types of addressing modes. Answer:To reference alarge range of locationsinmainmemory,avarietyof addressingtechnique are used.The commonaddressingmodesare: Immediate Direct Indirect Register Registerindirect 3. Describe the logical layout of both RISC and CISC computers Answer : An important aspect of computer architecture is the design of the instruction set for the processor. The instruction set chosen for a particular computer determines the way that machine language programs are constructed. Early computers had small and simple instruction sets, forced

- 2. mainlybythe needtominimize the hardware usedtoimplementthem.Asdigital hardware became cheaper with the advent of integrated circuits, computer instructions tended to increase both in number and complexity. Many computers have instruction sets that include more than 100 and sometimes even more than 200 instructions. These computers also employ a variety of data types and a large number of addressing modes. 4. Explain the concept of branch handling. What is delayed branching? Answer:A branch isan instructionina computerprogramthat may, whenexecuted by a computer, cause the computer to begin execution of a different instruction sequence. Branch (or branching, branched) mayalsoreferto the act of beginning executionof adifferentinstructionsequence dueto executing a branch instruction. A branch instruction can be either an unconditional branch, which always results in branching, or a conditional branch, which may or may not cause branching depending on some condition. When executing (or "running") a program, a computer will fetch and execute instructions in sequence (in their order of appearance in the 5. Explain any five types of vector instructions in detail. Answer : five types of vector instructions are below : 1. Elemental Vector Operations The Cray X1 systemvectorinstructionset contains vector versions of most scalar integer functions, floating-pointfunctions,and memory references. These elemental vector operations process each element independently. They execute under control of a mask register (m0,...,m3) and the vector length register (vl). Though there are 8 mask registers, only the first 4 can be used in the vector instructions. The assembler's default controlling mask register is m0. By software convention, every bit in m0 is always set. 6 Write short notes on: a) UMA Answer: Uniform memory access (UMA) is a shared memory architecture used in parallel computers. All the processors in the UMA model share the physical memory uniformly. In a UMA architecture, access time to a memory location is independent of which processor makes the request or which memory chip contains the transferred data. Uniform memory access computer architectures are often contrasted with non-uniform memory access (NUMA) architectures. In the UMA architecture, each processor may b) NUMA Answer: NUMA (non-uniform memory access) is a method of configuring a cluster of microprocessor in a multiprocessing system so that they can share memory locally, improving performance and the ability of the system to be expanded. NUMA is used in a symmetric multiprocessing( SMP) system.AnSMPsystemisa "tightly-coupled," "share everything" system in

- 3. which multiple processors working under a single operating system access each other's memory overa common busor "interconnect"path.Ordinarily,alimitationof SMPisthat as microprocessors are added, the shared bus or data path get overloaded and becomes a performance bottleneck. NUMA adds an intermediate level of memory Dear students get fully solved assignments Send your semester & Specialization name to our mail id : “ help.mbaassignments@gmail.com ” or Call us at : 08263069601