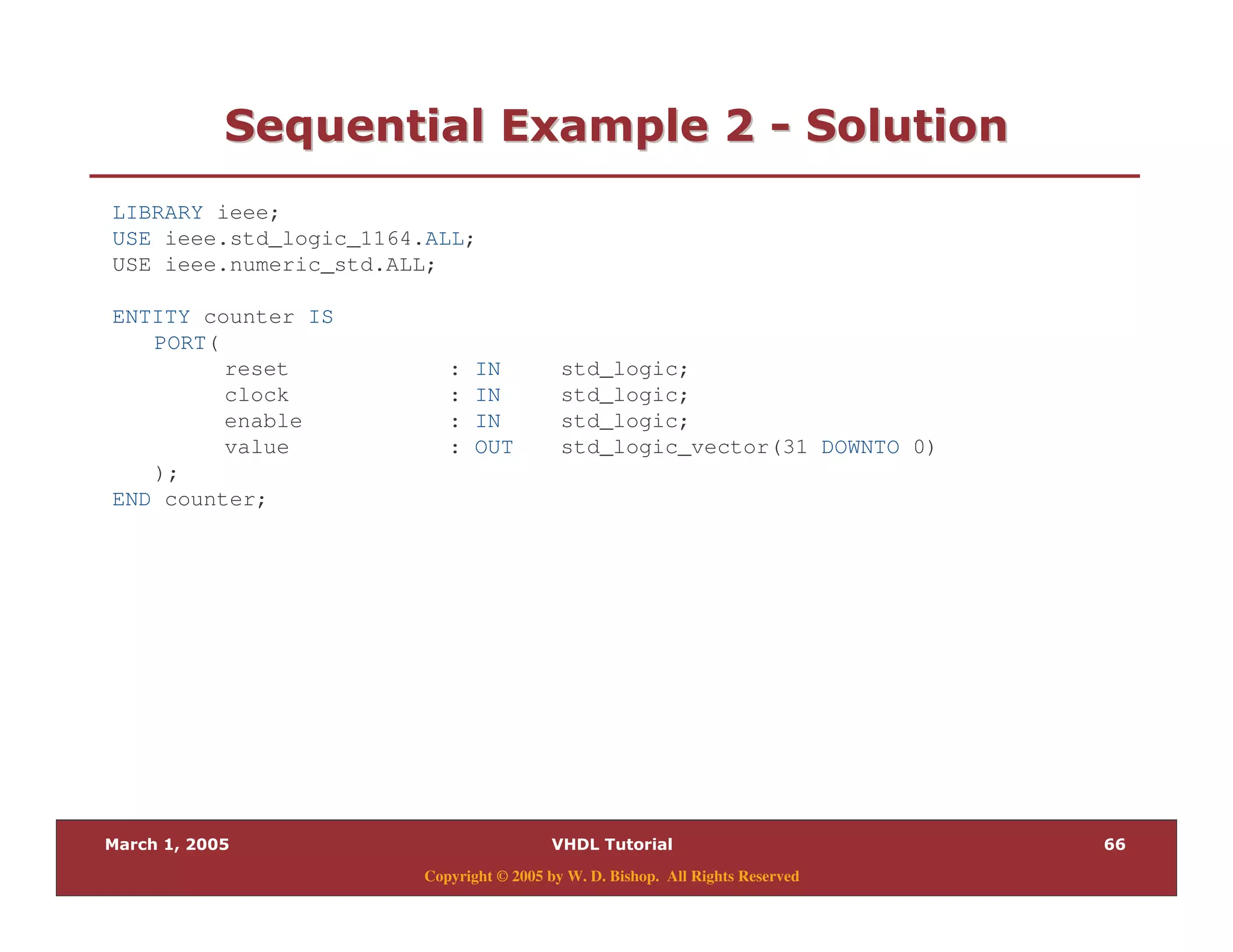

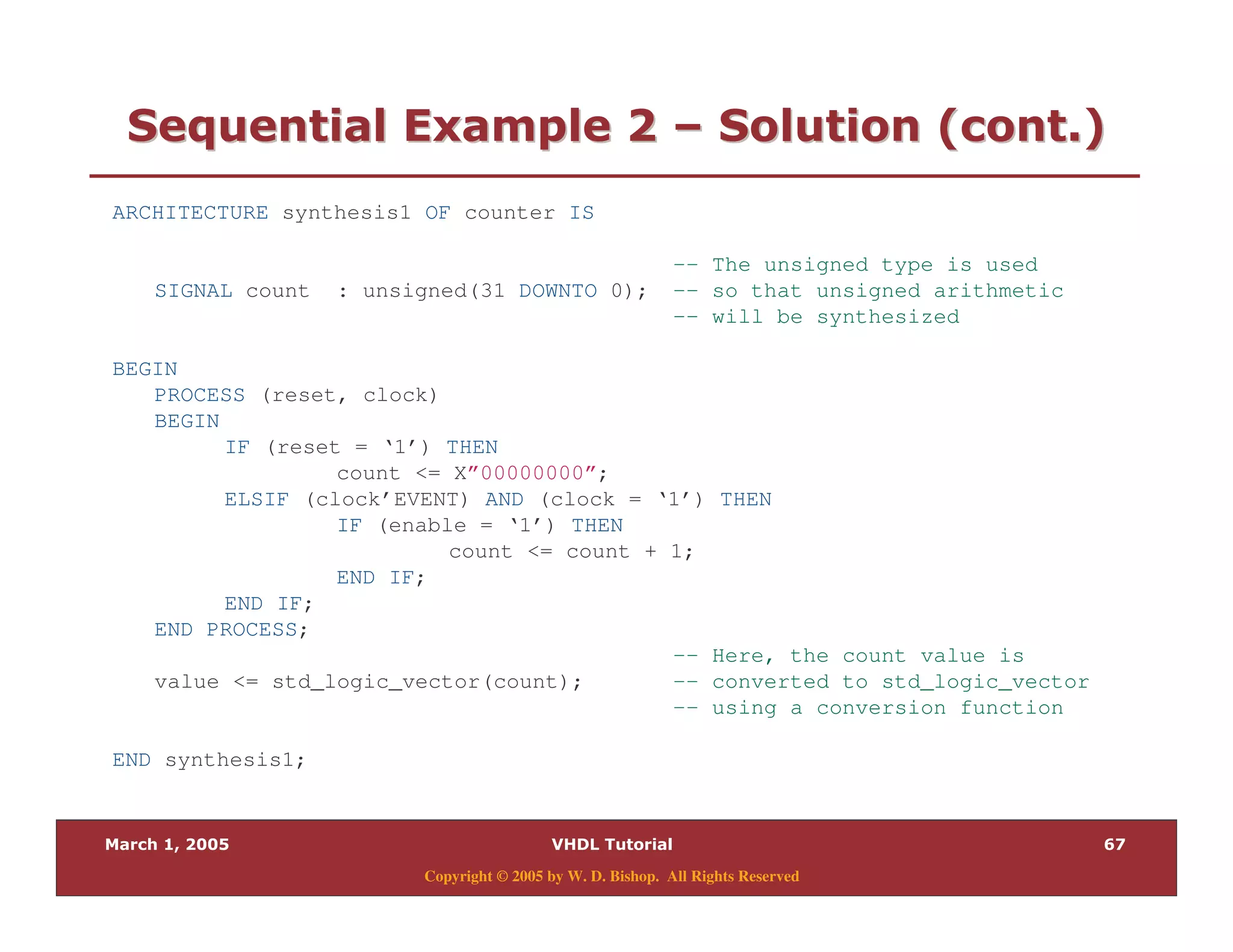

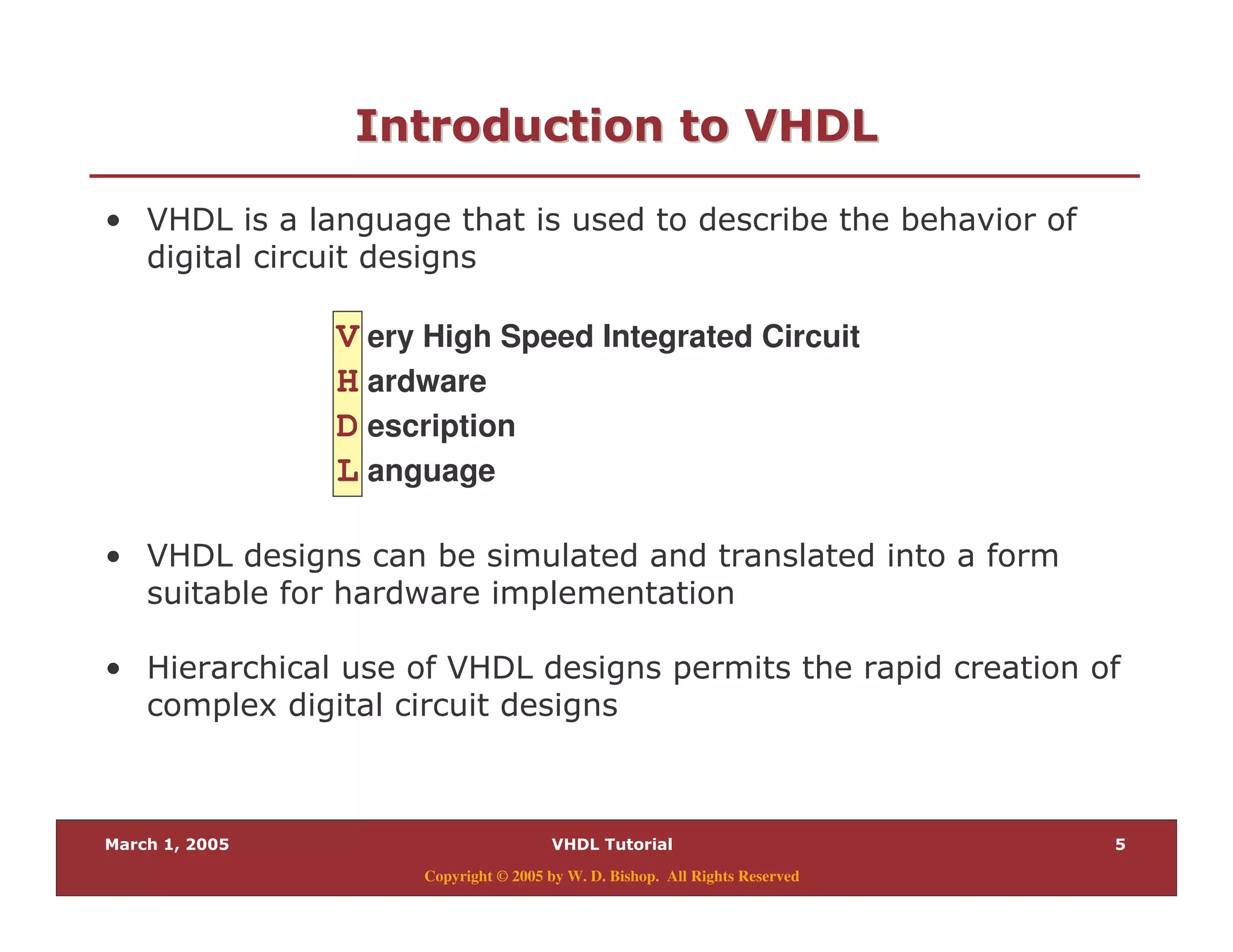

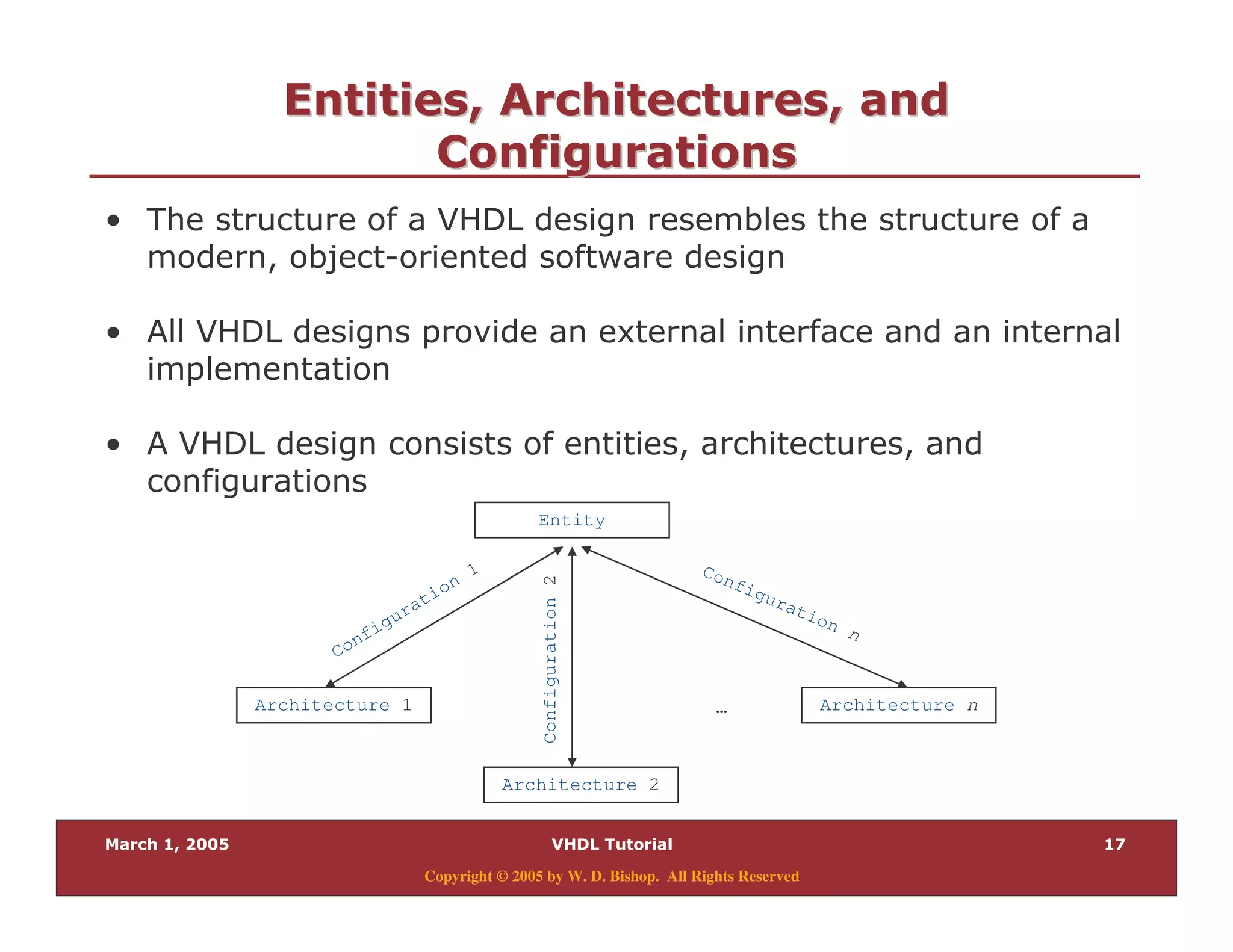

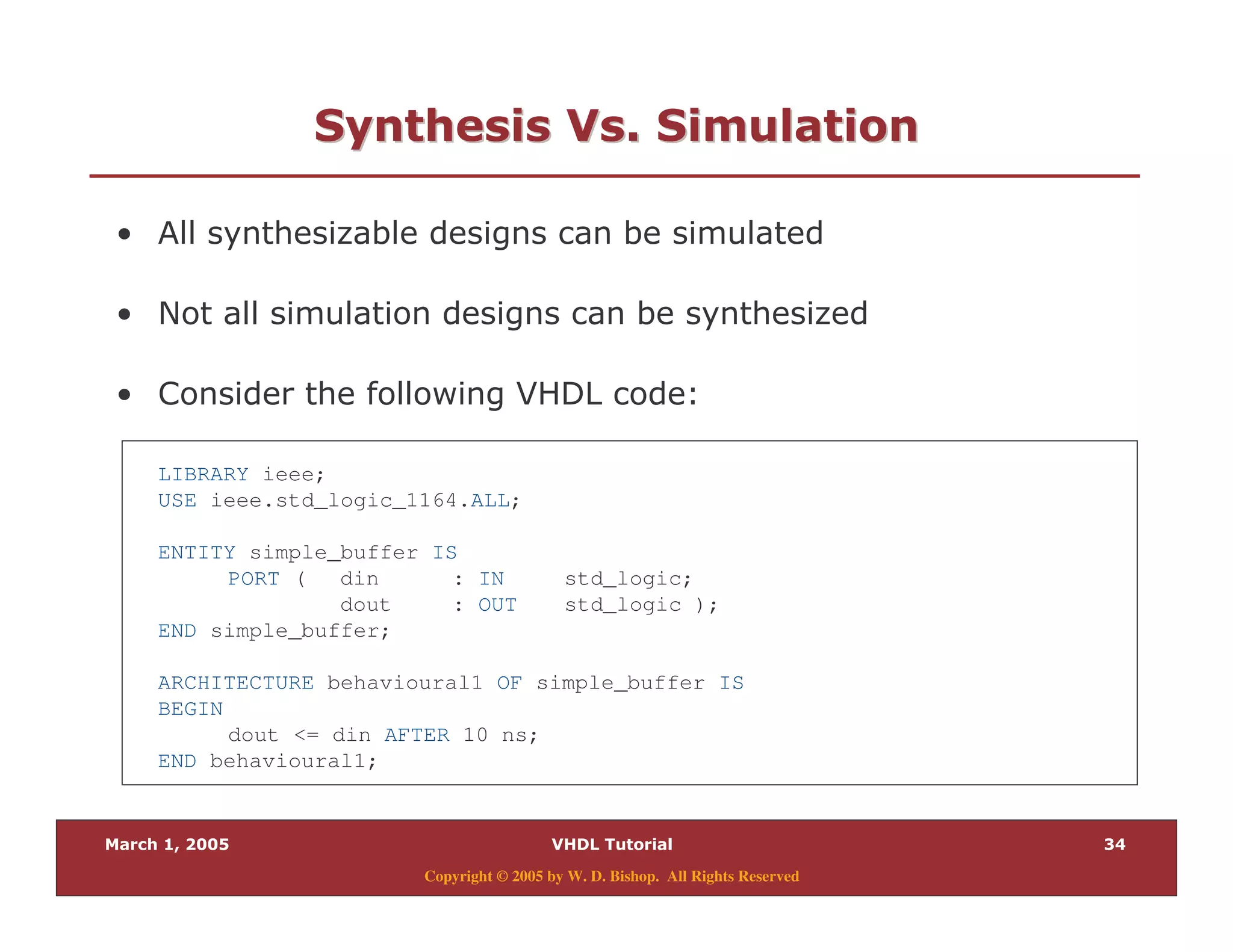

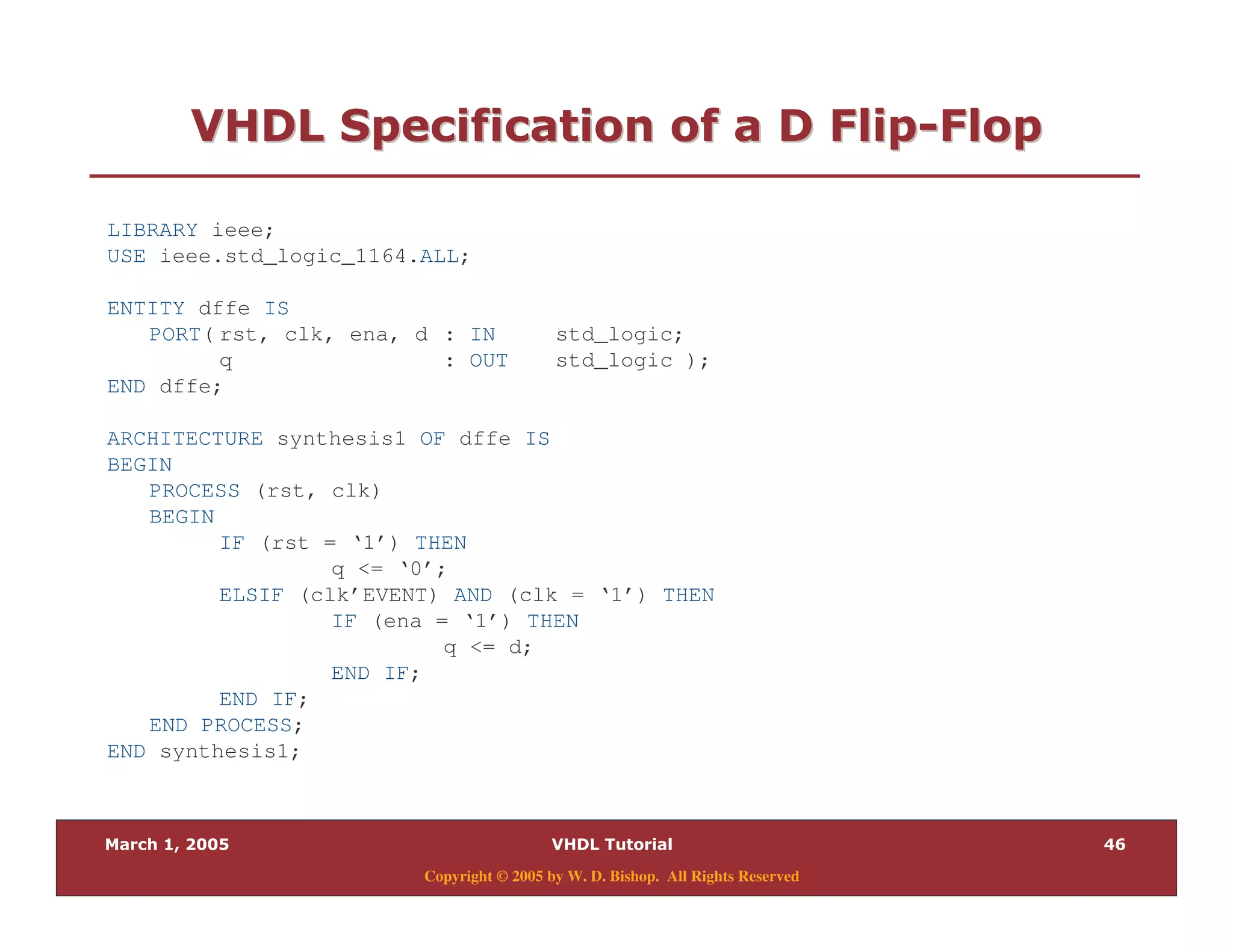

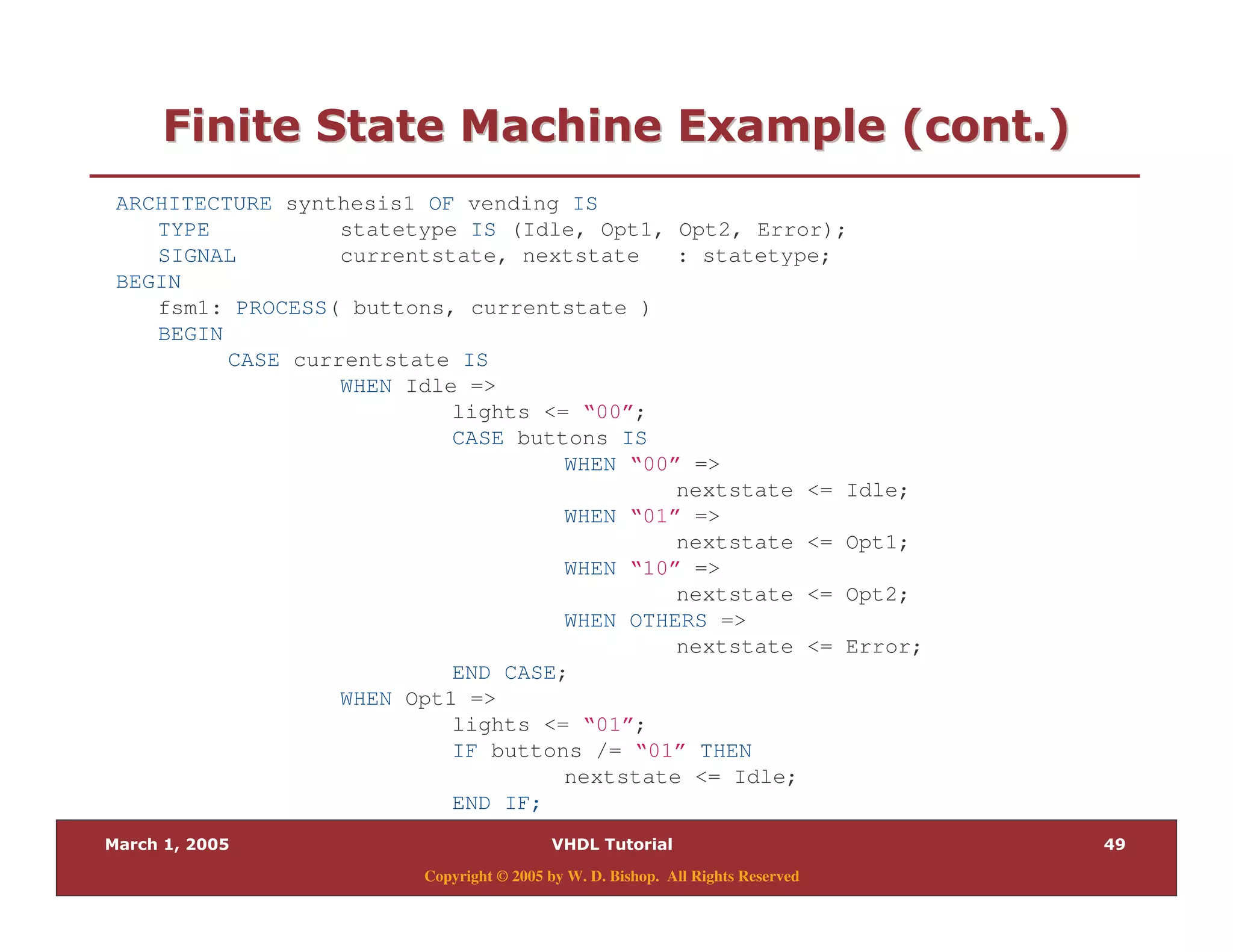

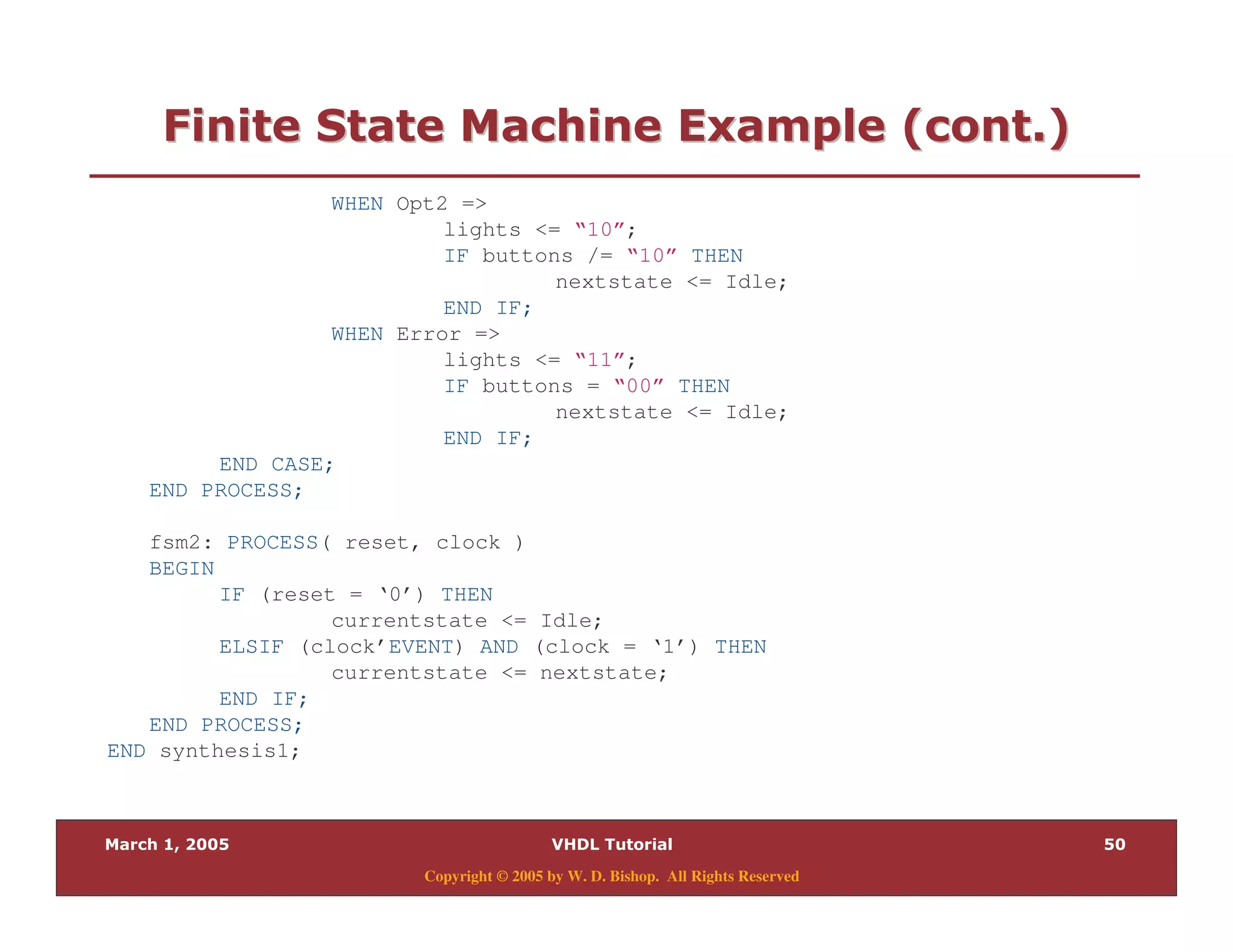

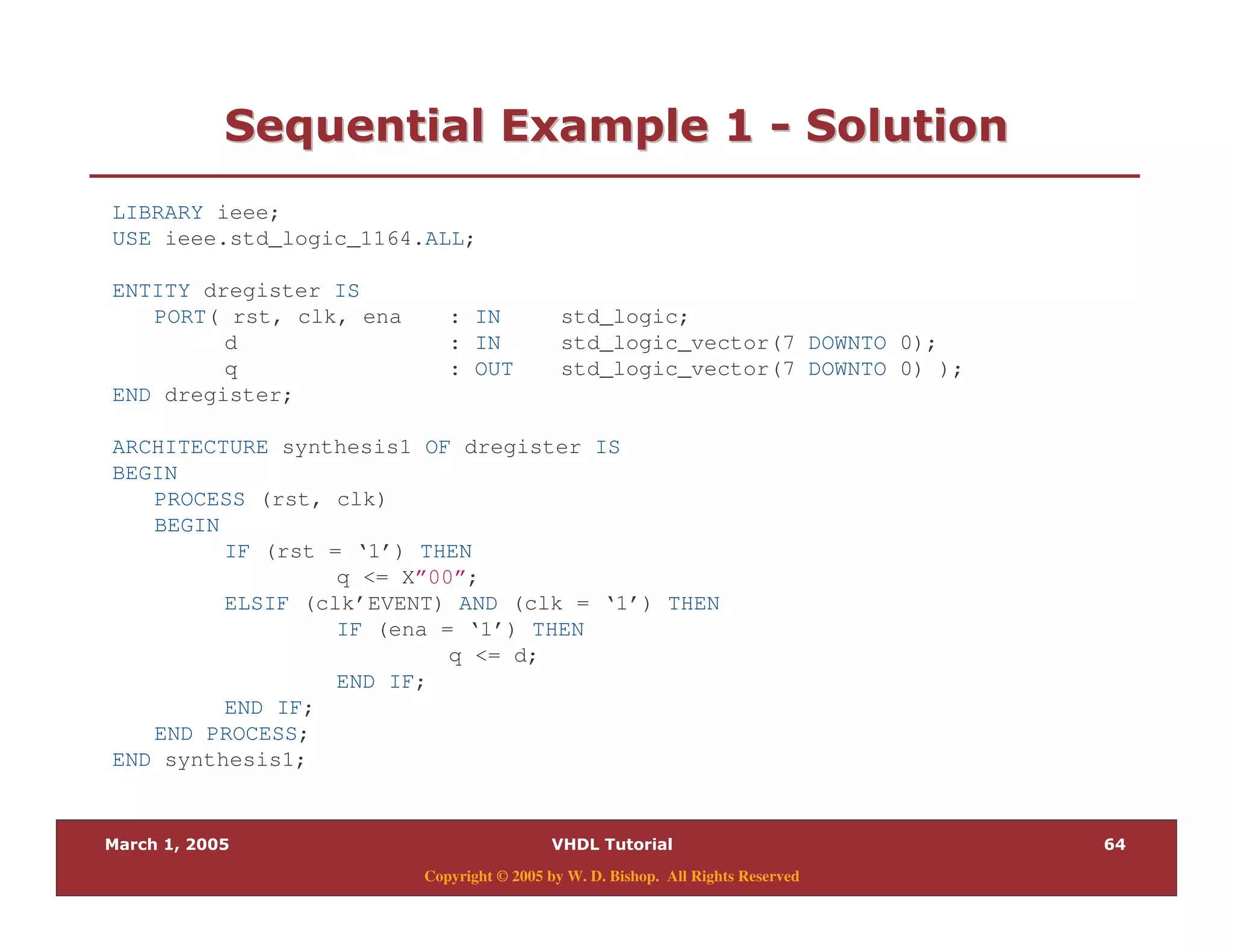

This document provides an introduction and overview of VHDL (VHSIC Hardware Description Language). It defines VHDL, describes its uses for hardware description and simulation, and outlines some key components of VHDL including entities, architectures, configurations, processes, signals, and concurrent signal assignments. It also provides examples of VHDL code for simple logic gates and sequential logic.

![.

Copyright © 2005 by W. D. Bishop. All Rights Reserved

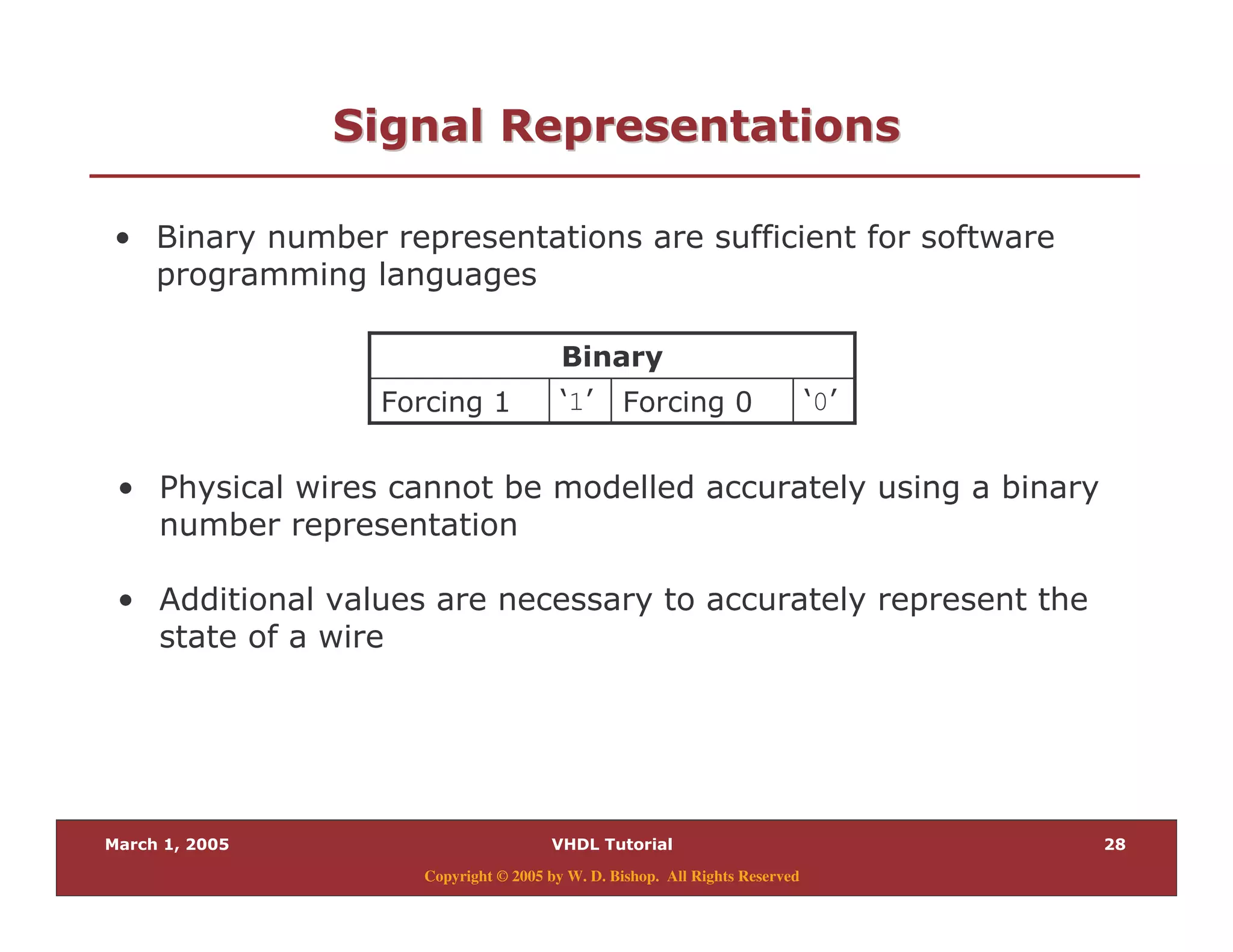

/ " " 28/ " " 28

%

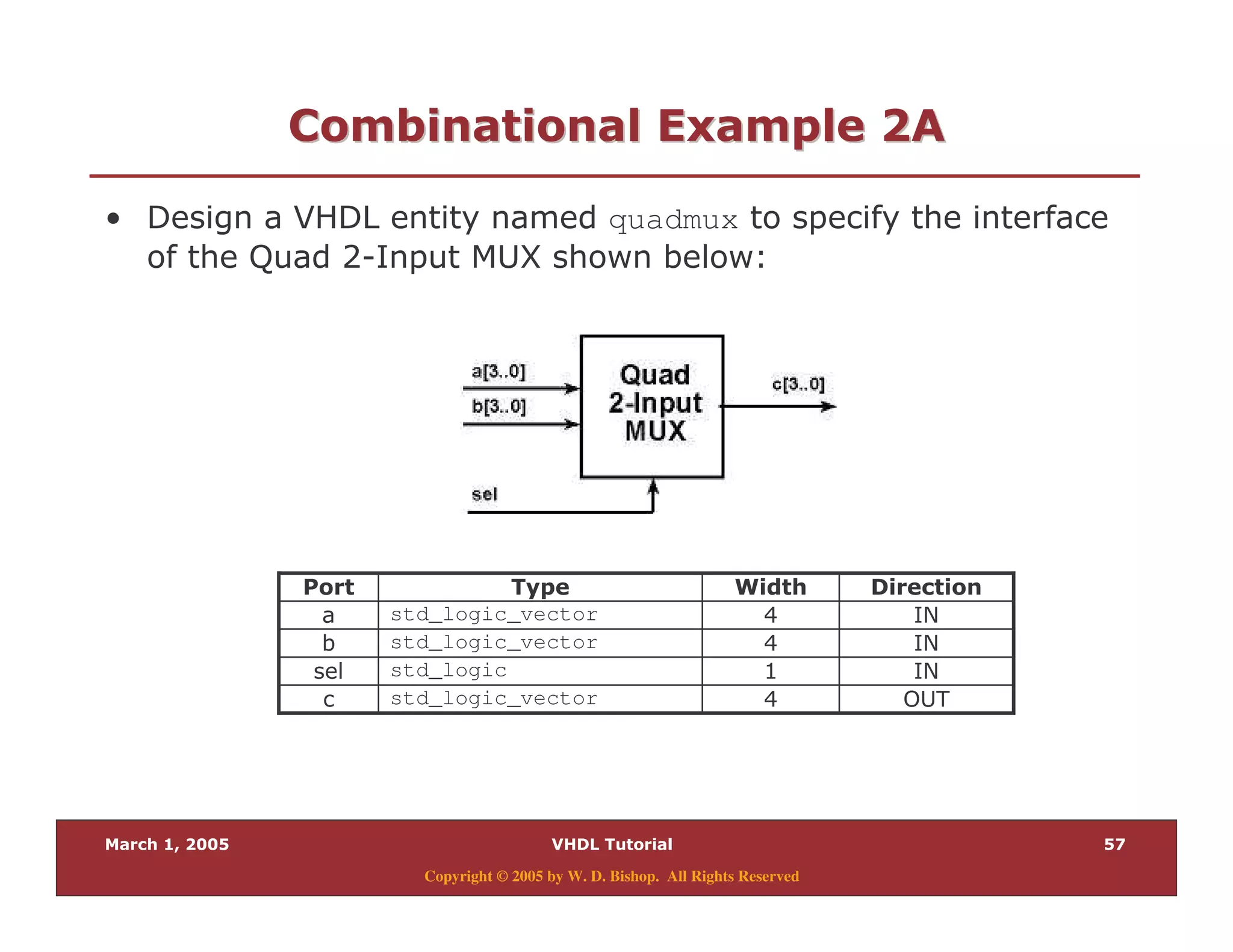

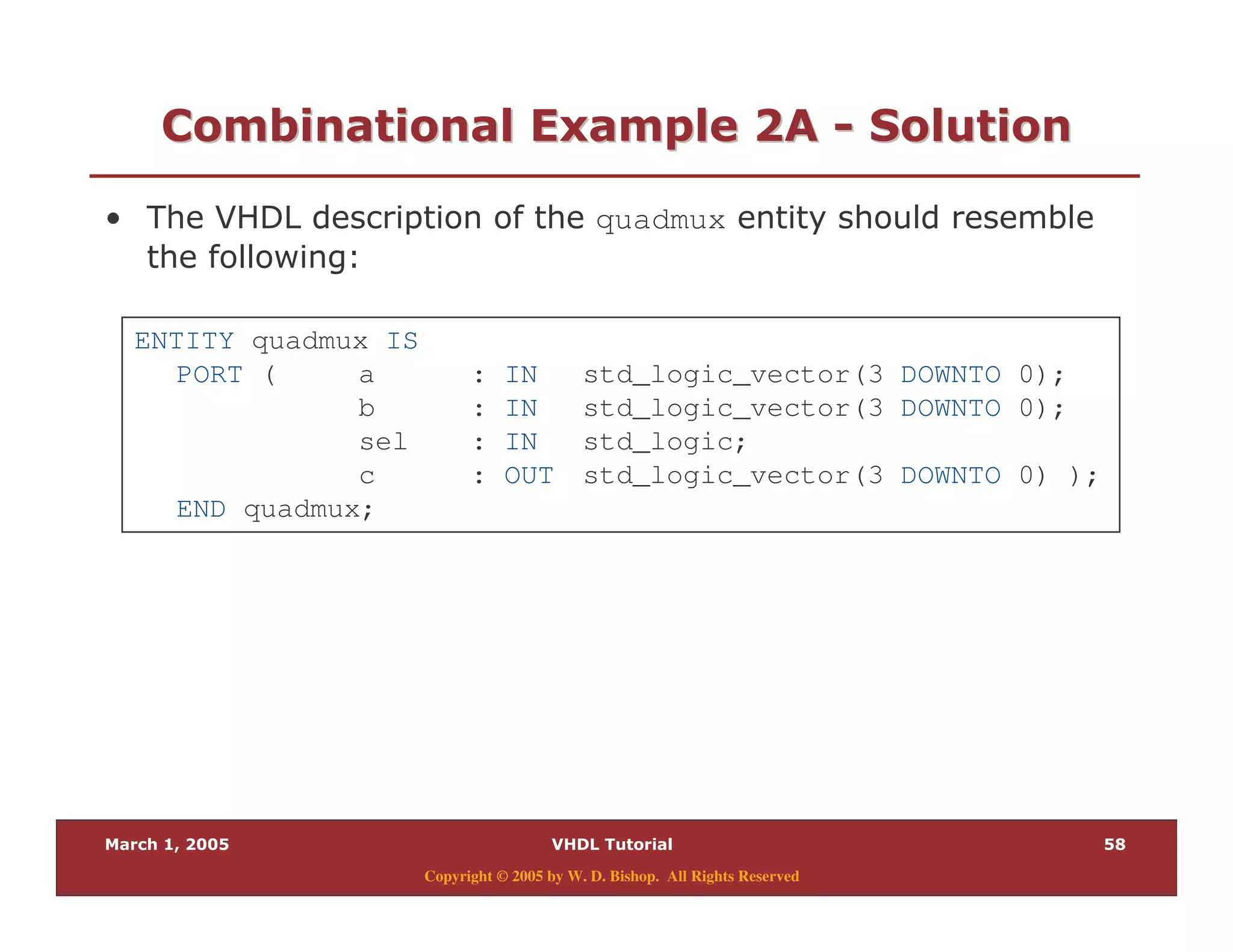

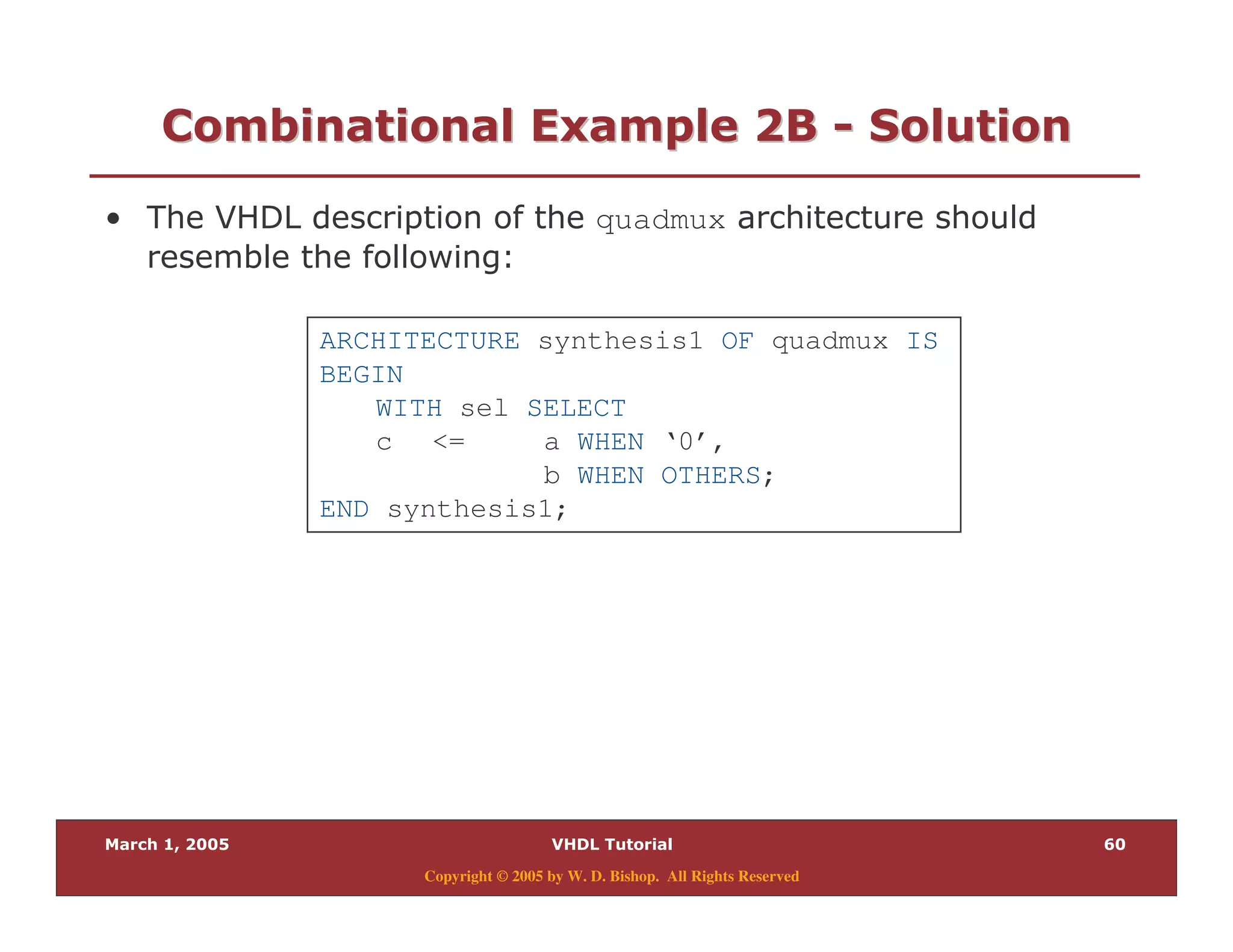

quadmux

% ? # ;9 P &

$

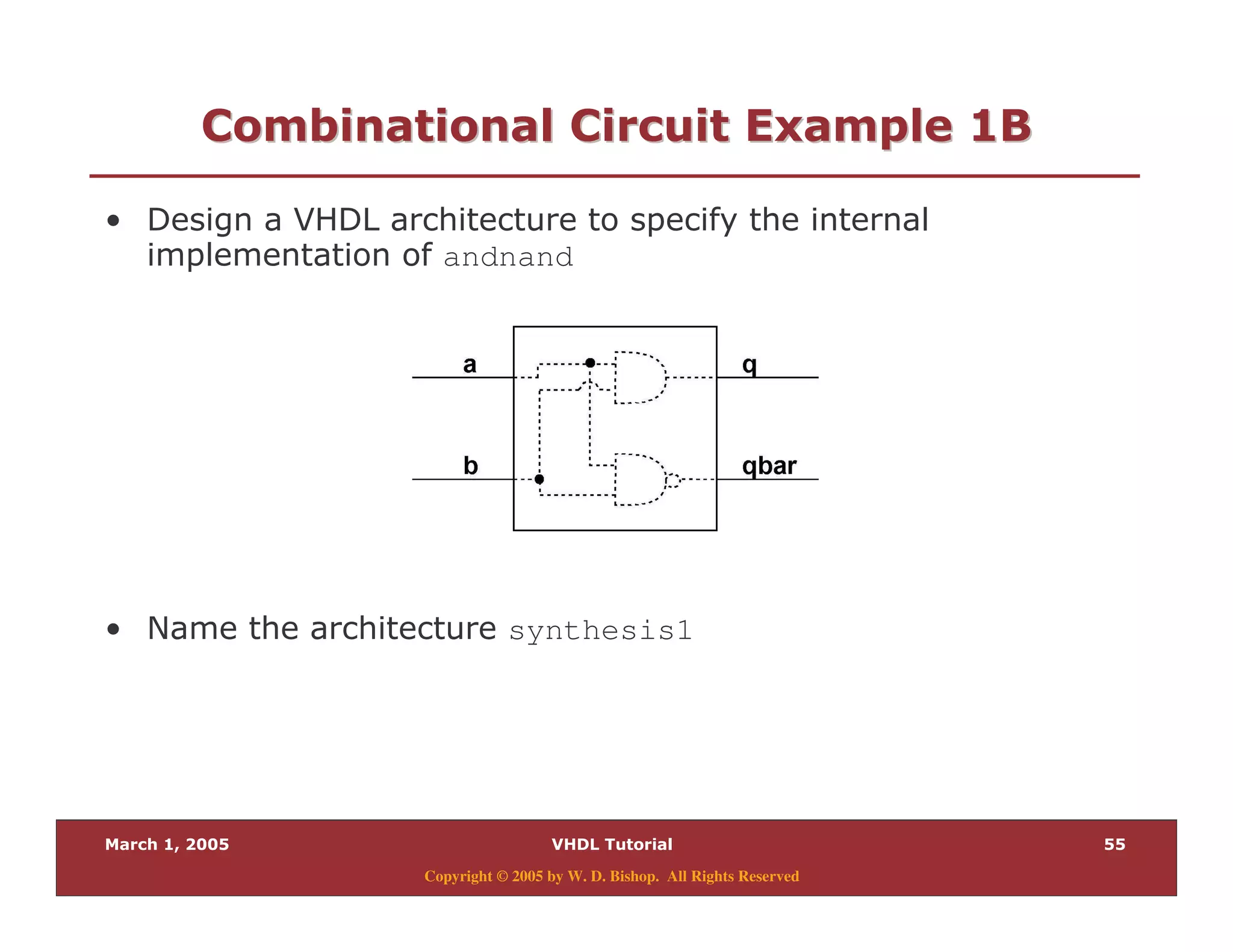

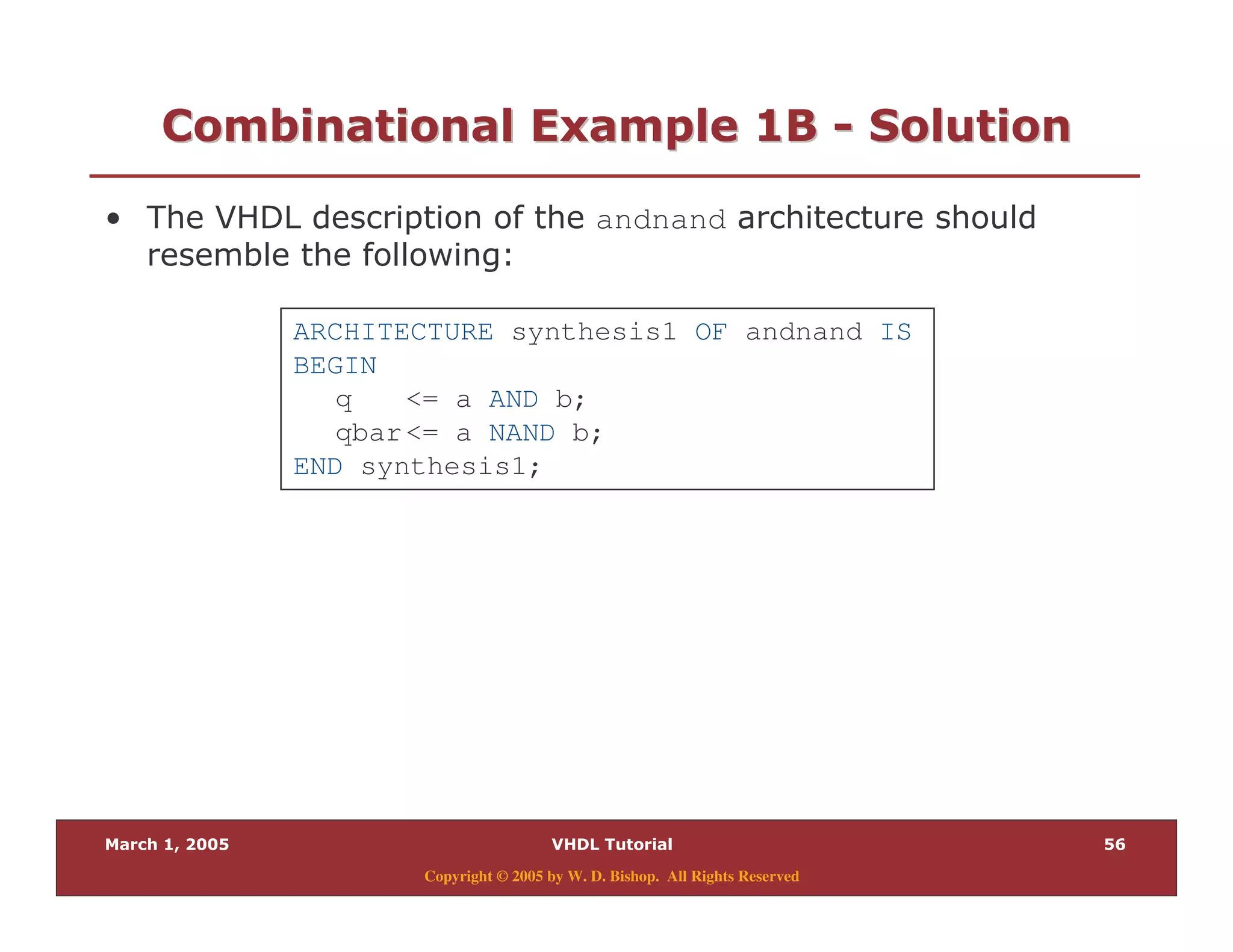

% < synthesis1

b[3..0]1

a[3..0]0

c[3..0]sel](https://image.slidesharecdn.com/vhdl2005-audio-150914111215-lva1-app6891/75/Vhdl-ppt-59-2048.jpg)

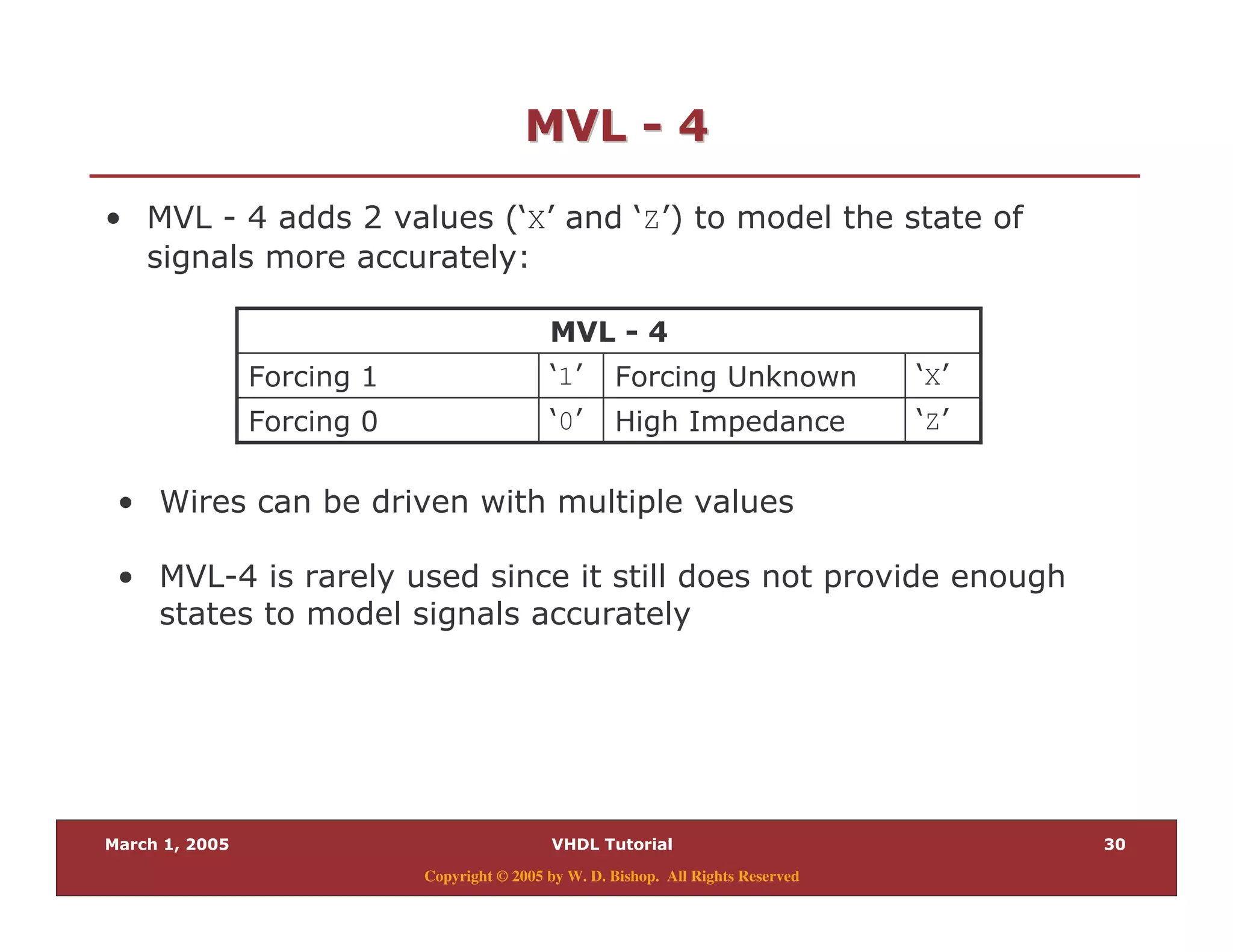

![(

Copyright © 2005 by W. D. Bishop. All Rights Reserved

0 = " 280 = " 28

% ) :;9

&

% , :;9 & &$

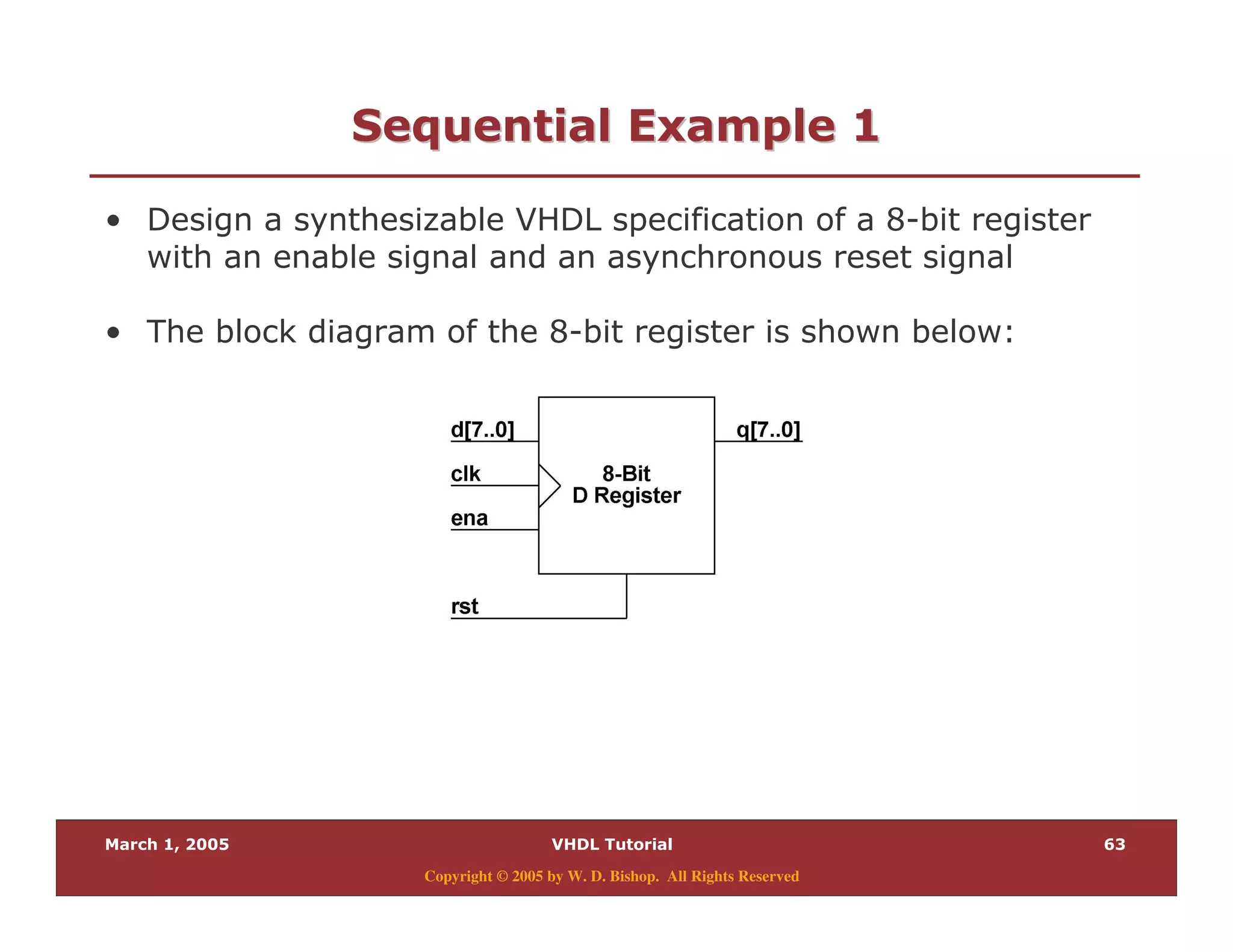

32-Bit Counter

value[31..0]reset

enable

clock](https://image.slidesharecdn.com/vhdl2005-audio-150914111215-lva1-app6891/75/Vhdl-ppt-65-2048.jpg)