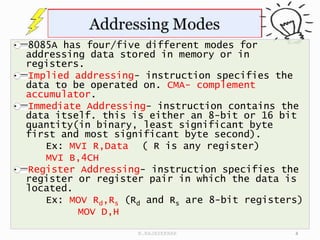

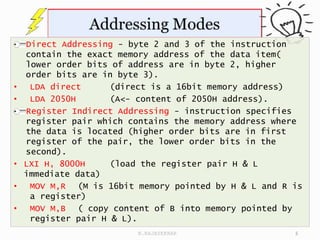

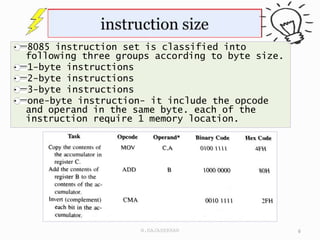

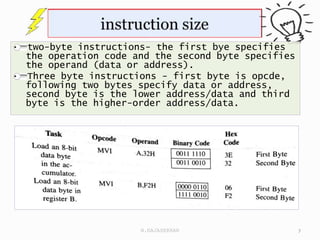

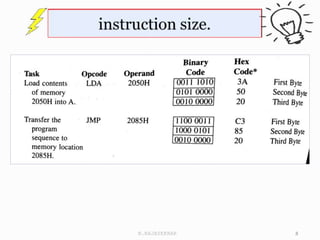

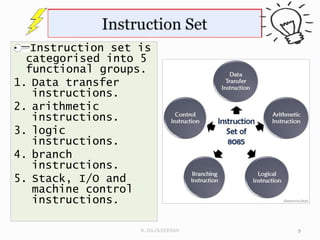

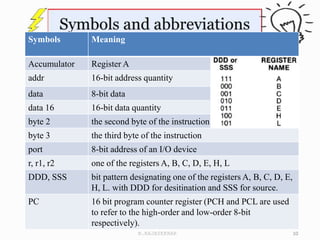

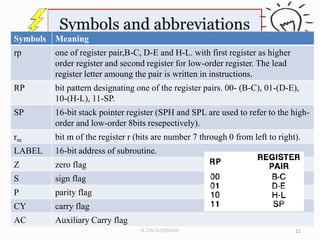

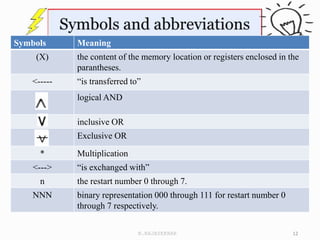

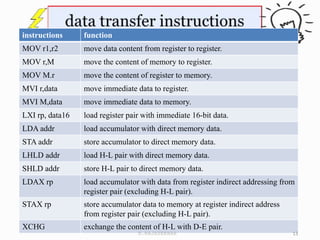

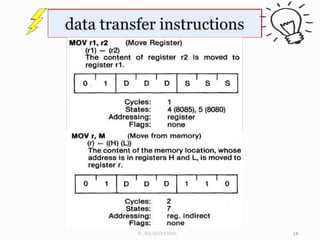

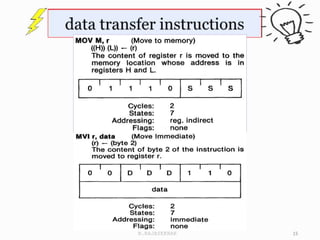

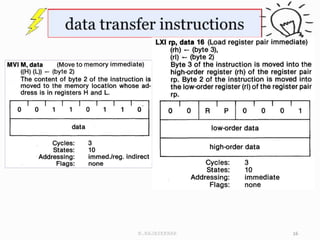

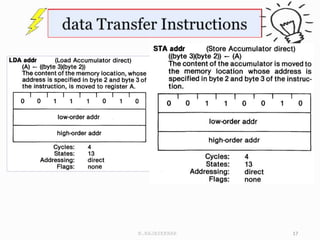

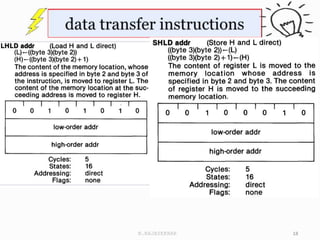

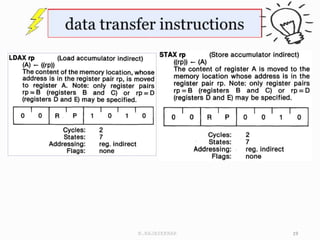

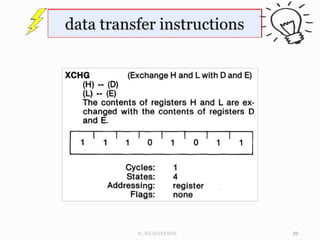

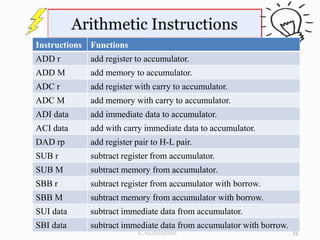

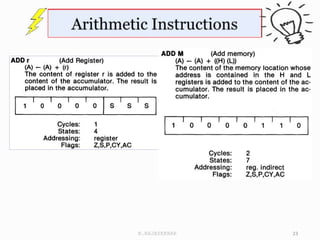

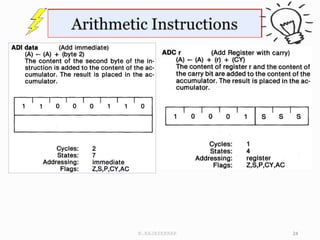

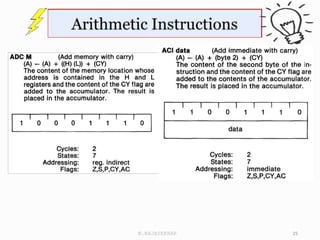

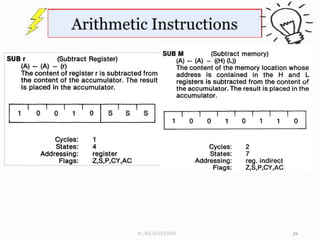

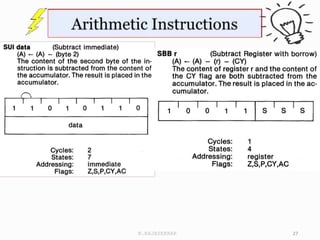

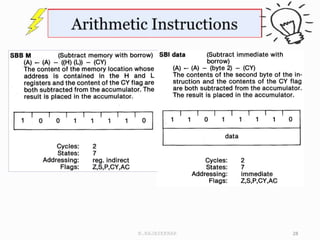

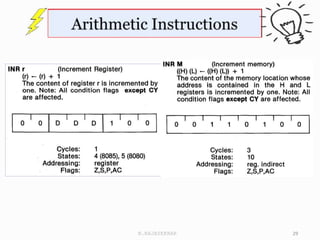

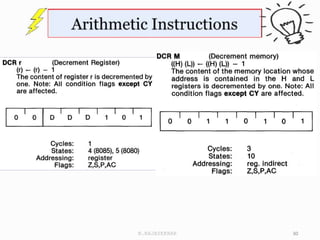

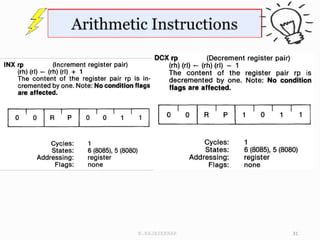

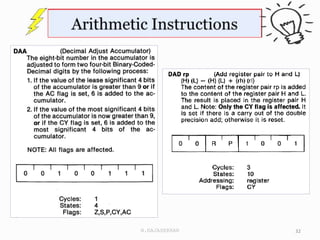

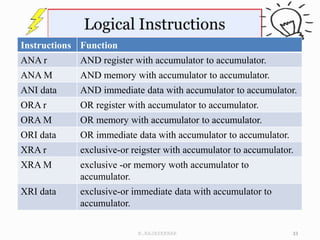

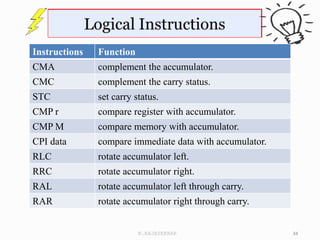

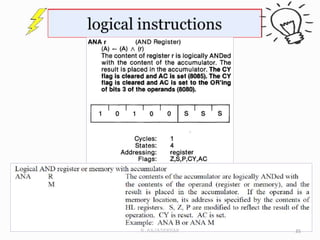

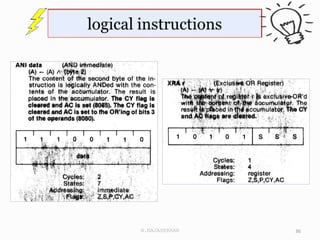

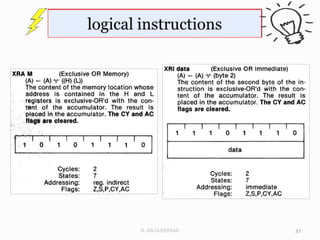

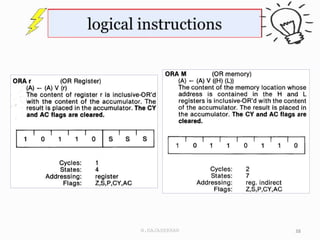

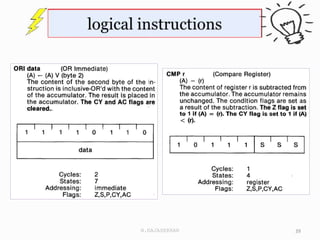

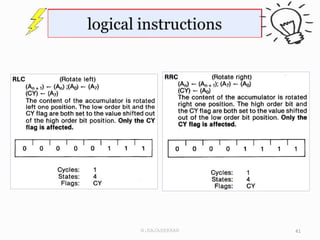

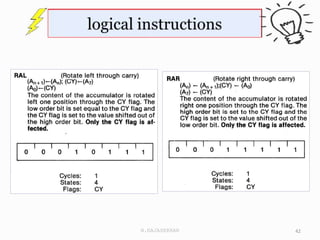

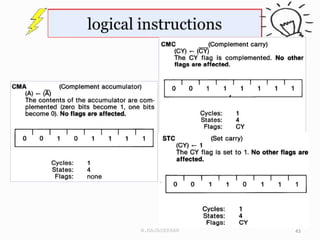

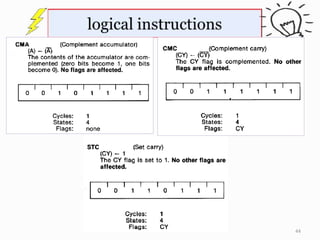

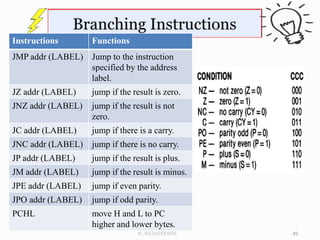

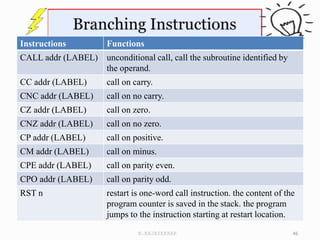

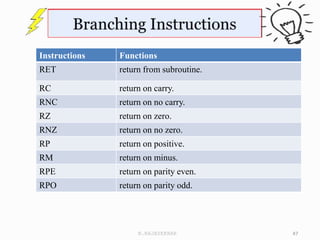

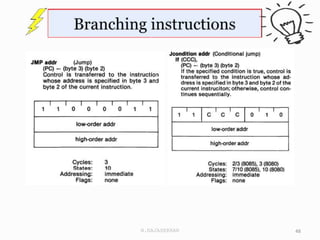

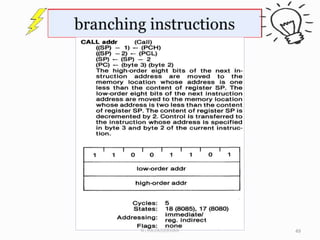

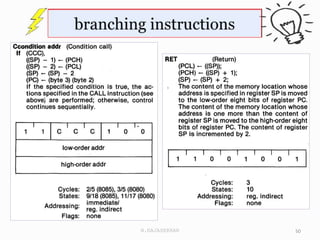

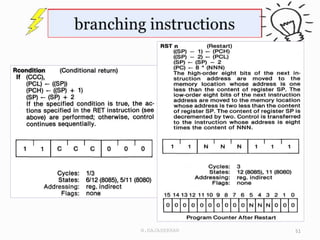

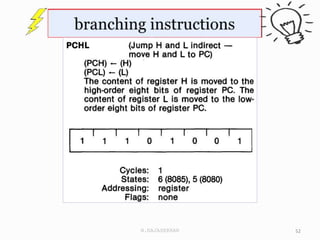

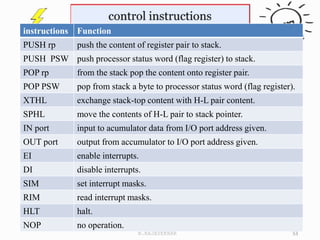

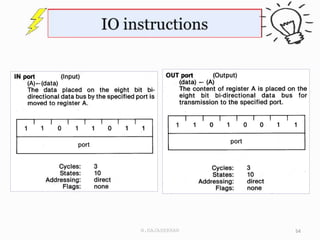

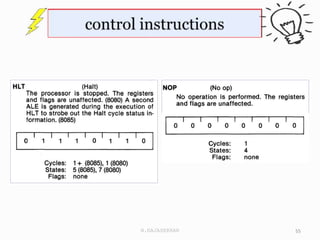

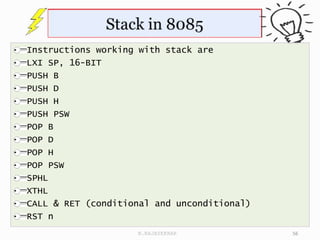

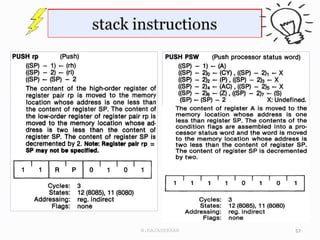

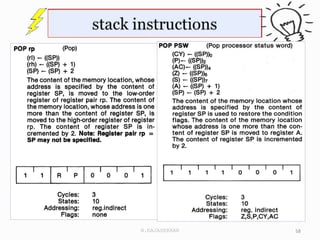

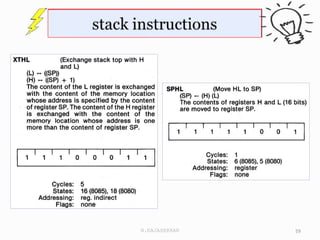

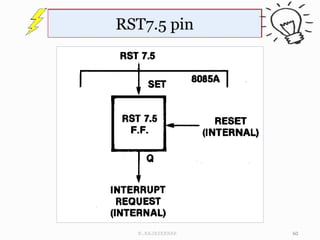

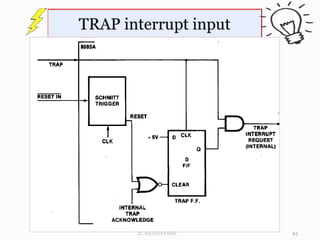

The document discusses the 8085 microprocessor. It covers addressing modes, data formats, instruction sets, interrupts, and provides examples of programming the 8085 microprocessor. It describes one-byte, two-byte and three-byte instructions and categorizes the instruction set. It also defines various symbols used and provides details of data transfer, arithmetic, logic, branch, and machine control instructions.