Technology used for memory final.pptx

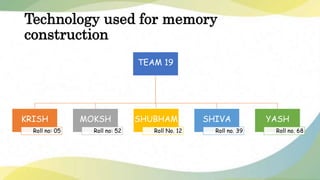

- 1. Technology used for memory construction TEAM 19 KRISH Roll no: 05 MOKSH Roll no: 52 SHUBHAM Roll No. 12 SHIVA Roll no. 39 YASH Roll no. 68

- 2. What is Memory? Memory is the electronic holding place for the instructions and data a computer needs to reach quickly. It's where information is stored for immediate use. Memory is one of the basic functions of a computer, because without it, a computer would not be able to function properly. Memory is also used by a computer's operating system, hardware and software. Memory construction in digital electronics is the process of designing and building circuits that can store and retrieve binary information. The basic building block of memory is the memory cell, which can store a single bit of data. Memory cells are typically arranged in arrays, with each row of cells representing a machine word. What is Memory Construction?

- 6. WELL FORMATION ISOLATION FORMATION TRANSISTOR MAKING INTERCONNECTION PASSIVATION PROCESS FLOW

- 7. CMOS FABRICATION PROCESS well formation • Start with clean p-type substrate (p-type wafer)

- 8. CMOS FABRICATION PROCESS well formation • Grow epitaxy layer (made from SiO2) as mask layer for well formation

- 9. CMOS FABRICATION PROCESS well formation • By *photolithography and etching process, well opening are made *photolithography and etch processes are shown in next slides Well will be formed here

- 10. Photolithography (CED) P-substrate Si02 photoresist • Photoresist coating (C) • Masking and exposure under UV light(E) • Resist dissolved after developed (D) • Pre-shape the well pattern at resist layer P-substrate mask UV light Opaque area Transparent area

- 11. etching • Removing the unwanted pattern by wet etching • Resist clean • Desired pattern formed P-substrate P-substrate

- 12. CMOS FABRICATION PROCESS well formation • Ion bombardment by ion implantation • SiO2 as mask, uncovered area will exposed to dophant ion Phosphorus ion

- 13. CMOS FABRICATION PROCESS: Isolation Formation • Increase SiO2 thickness by oxidation at high temperature • Oxide will electrically isolates nmos and pmos devices Thick oxide

- 14. CMOS FABRICATION PROCESS transistor making • By photolithography and etching process, pmos and nmos areas are defined pmos will be formed here nmos will be formed here LOCOS (isolation structure)

- 15. CMOS FABRICATION PROCESS transistor making • Grow very thin gate oxide at elevated temperature in very short time Gate oxide

- 16. • Deposit polisilicon layer CMOS FABRICATION PROCESS transistor making polisilicon

- 17. • Photolithography (photo) and etching to form gate pattern CMOS FABRICATION PROCESS transistor making gate

- 18. CMOS FABRICATION PROCESS transistor making • Photo process to define the nmos’s active (source and drain) area and VDD contact • Ion implantation with Arsenic ion for n+ dophant. • Photoresist and polisilicon gate act as mask photoresist Arsenic ion

- 19. CMOS FABRICATION PROCESS transistor making • Nmos’s Source and drain with VDD contact formation • Resist removal source drain VDD contact

- 20. CMOS FABRICATION PROCESS transistor making • Photo process to define the GND contact and pmos’s active area (source and drain) • Ion implantation with boron ionto have p+ dophant • Photoresist and gate act as mask Boron ion photoresist

- 21. CMOS FABRICATION PROCESS transistor making • Pmos’s source and drain formation with GND contact • Resist removal GND contact Pmos’ source Pmos’s drain

- 22. CMOS FABRICATION PROCESS interconnection • Deposit SiO2 layer through out wafer surface SiO2

- 23. • Photo and etching process to make contact CMOS FABRICATION PROCESS interconnection contact

- 24. • Metal 1 deposition throughout wafer surface CMOS FABRICATION PROCESS interconnection Metal 1

- 25. CMOS FABRICATION PROCESS interconnection • Photo and etching processes to pattern interconnection

- 26. Mask Layout

- 27. Mask Layout

- 28. Mask Layout

- 29. Mask Layout

- 31. CMOS Fabrication • IC Packaging - we continue connecting all of our MOSFETS, Resistors, and Capacitors together using Metal layers and vias - once we're done, we need to connect our IC to the outside world. - we need to put the silicon die into a Package - an IC package performs the following functions 1) protects the die from the outside world (contamination, etc…) 2) translates the on-chip interconnect density (um) to the off-chip interconnect density (mm) 3) moves the heat from the die to the outside world so it can be dissipated - we need to put pads on the outermost metal layer for the package leads to connect to. - the interconnect that goes from the IC to the package is called Level 1 Interconnect

- 32. CMOS Fabrication • IC Packaging Wire Bond - The most widely used package interconnect is a wire bond. - This is a thin gold wire that connects the pads on the IC to the package leads - To accommodate a wire bond, we put pads around the perimeter of the IC - the pads are relatively large (100um x 100um)

- 33. CMOS Fabrication • IC Packaging Flip Chip - A higher performing and higher density interconnect is called a flip-chip bump - A bump is a sphere of solder that is used to connect pads on the IC to the package - The main advantage is that we can put an array of pads, instead of just pads around the perimeter - this allows many more pads to be placed on the same die area - the pads are still relatively large (100um x 100um)

- 34. CMOS Fabrication • IC Packaging Package Interconnect - the package itself has an interconnect which ultimately connects the packaged IC to the system PCB (Level 2) - the two most common types of Level 2 interconnect are: 1) Lead Frame 2) Ball Grid Array - once the die has been connected to the package interconnect, we put encapsulate it in a protective material (plastic, epoxy, etc….) - this provides the protection for the die and is what we typically see when we look at a packaged part (i.e., the black plastic) Wire-bond on a Lead Frame Wire-bond on a BGA Flip-Chip on a BGA