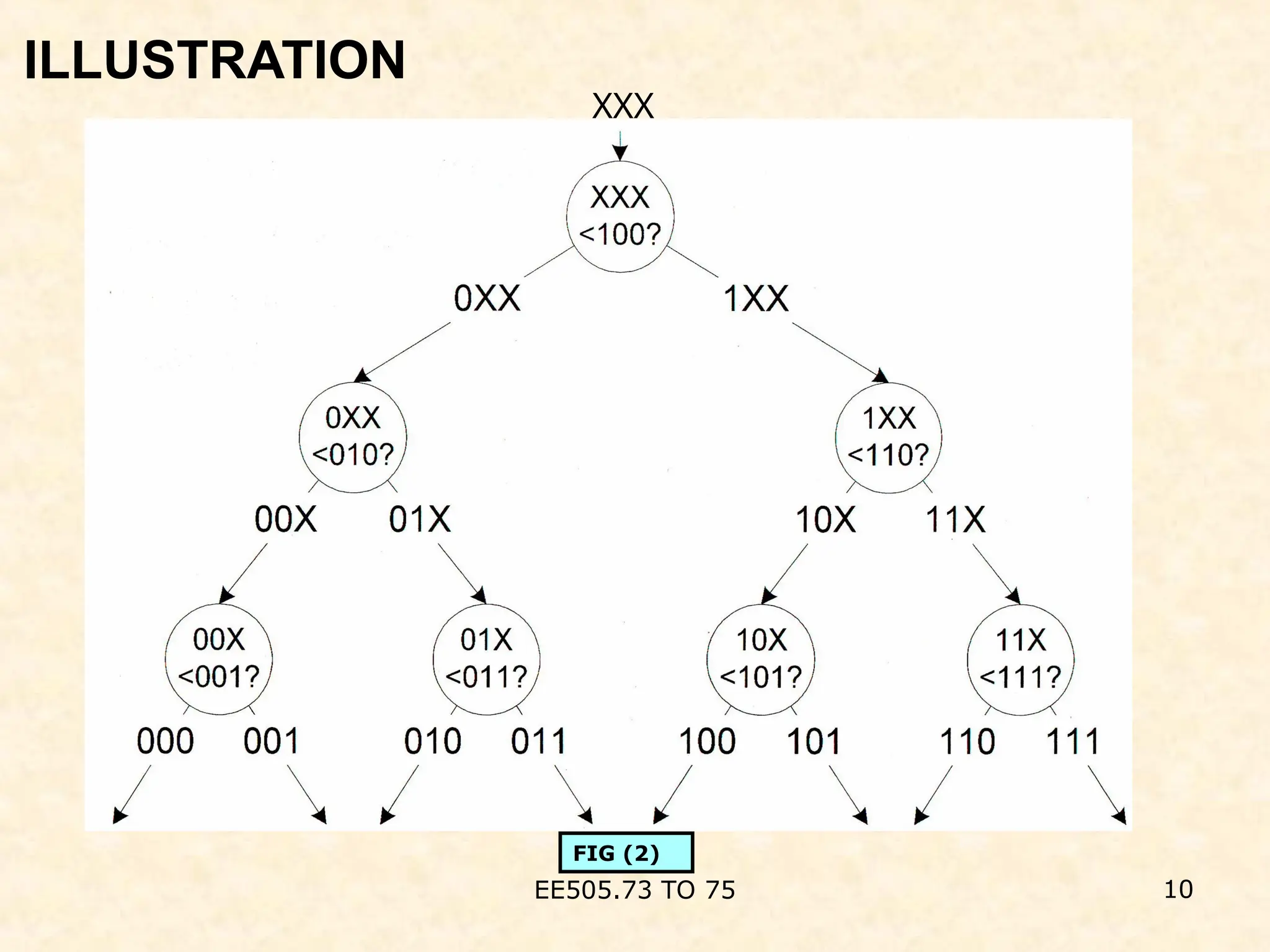

The document is a lecture outline for a course on digital electronics, specifically focusing on successive approximation analog-to-digital converters (ADCs). It covers the working mechanism, components, advantages, and includes a quiz and assignment related to the topic. Teaching aids such as PPT, block diagrams, and model graphs are also mentioned to facilitate learning.