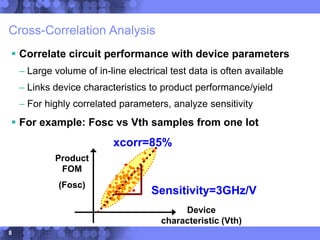

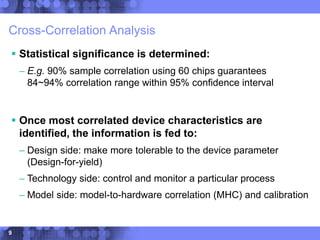

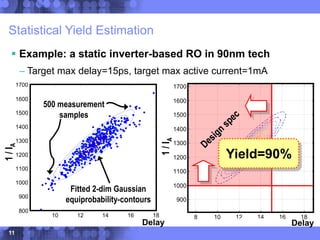

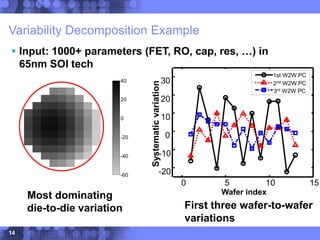

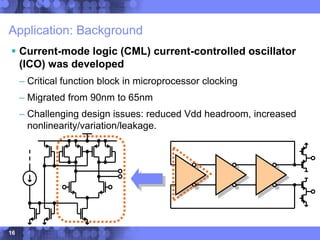

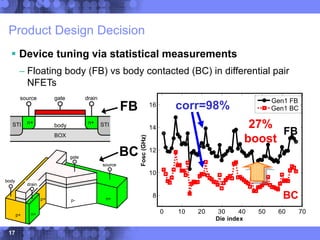

This document proposes a statistical framework for co-designing technology, models, and products. It includes three main components: cross-correlation analysis to link device characteristics to product performance; statistical yield estimation to predict yield using hardware data; and variability decomposition to separate systematic variability. The framework is applied to an integrated circuit oscillator product developed across three 65nm technology generations, improving yield from 47% to 99% while meeting design specifications.