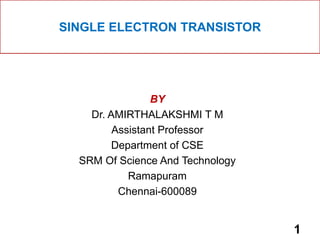

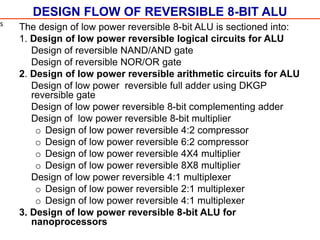

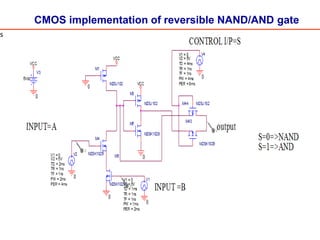

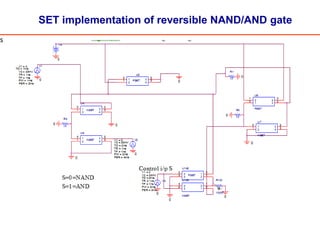

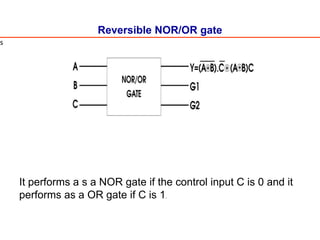

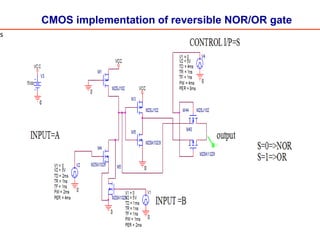

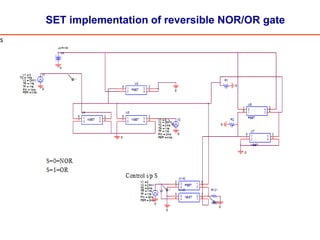

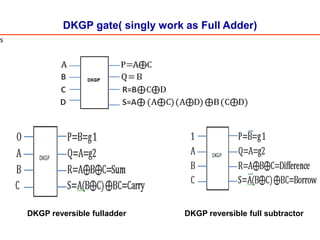

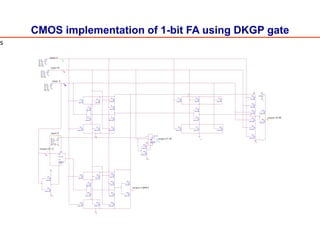

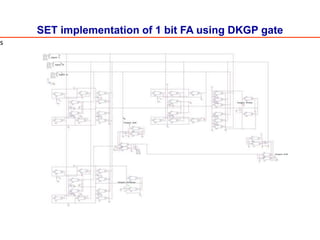

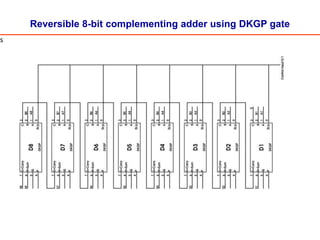

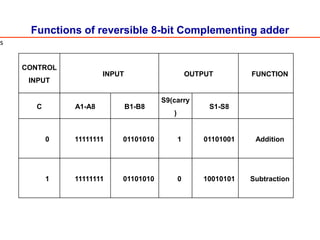

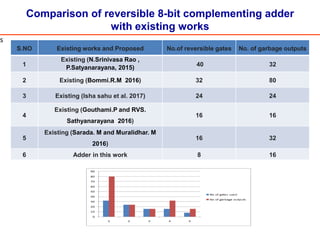

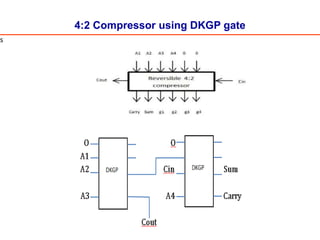

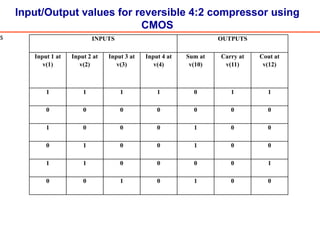

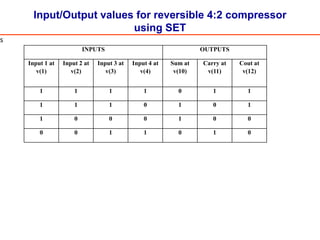

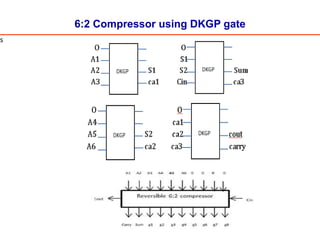

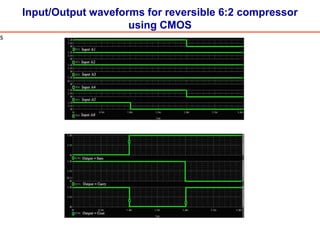

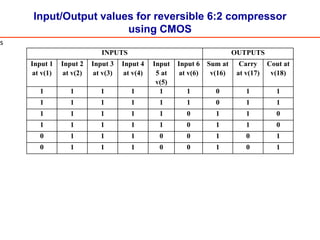

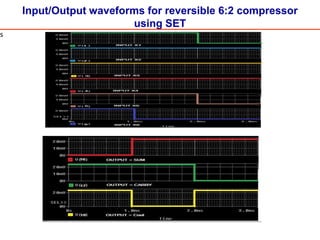

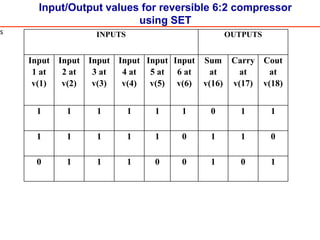

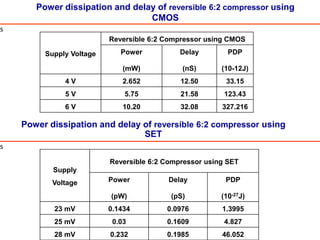

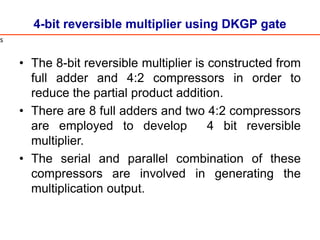

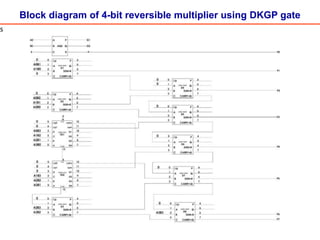

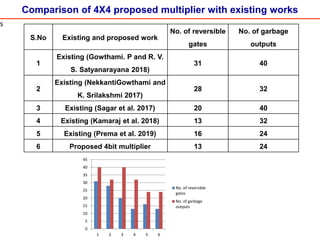

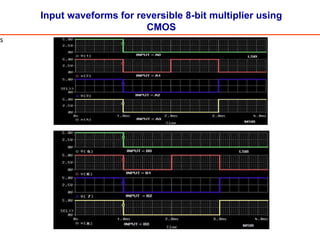

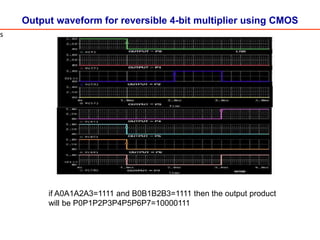

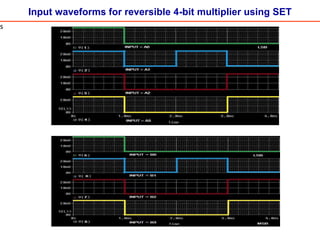

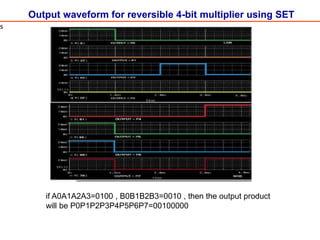

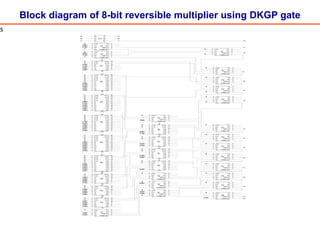

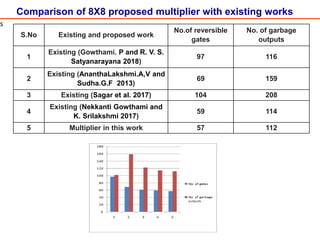

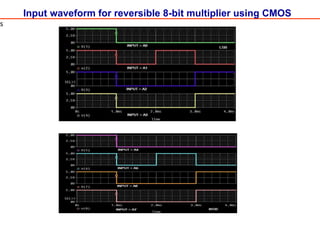

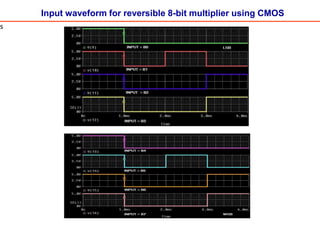

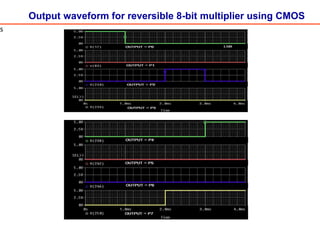

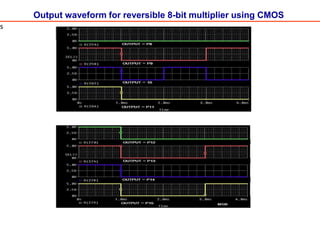

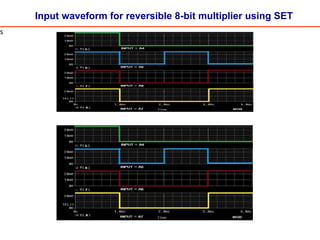

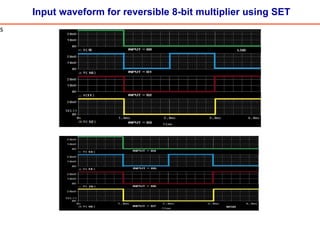

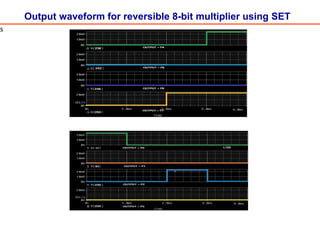

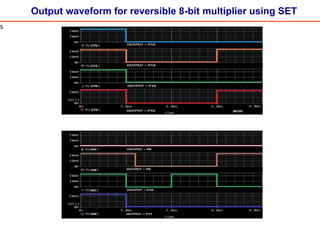

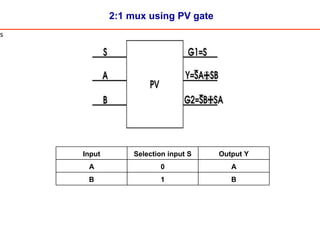

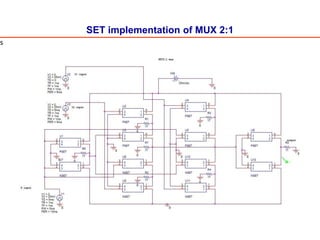

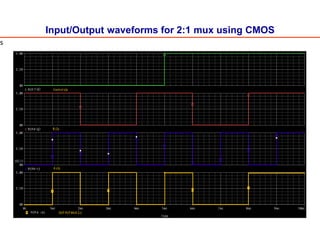

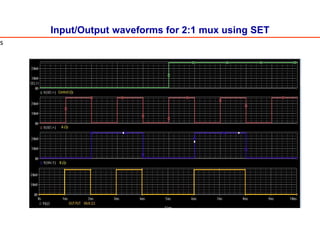

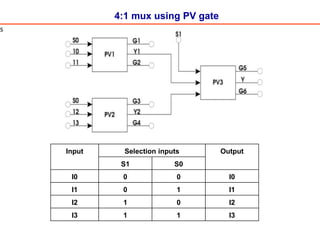

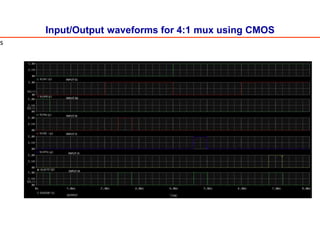

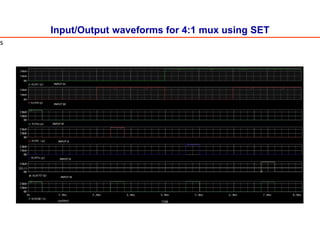

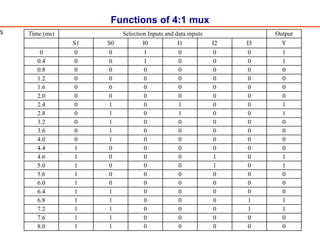

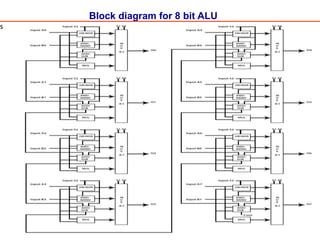

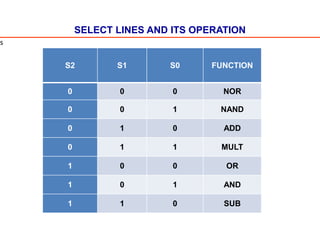

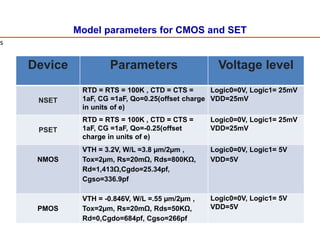

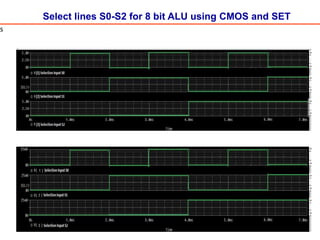

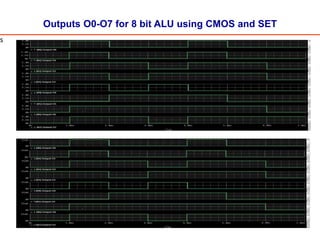

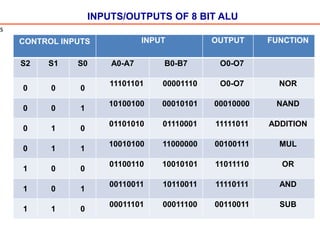

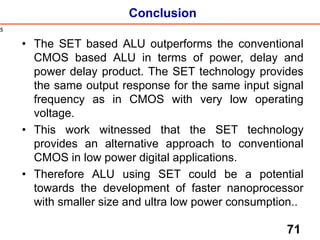

The document describes the design of a reversible 8-bit arithmetic logic unit (ALU) using low power reversible logic gates. It involves designing reversible logic gates, arithmetic circuits like full adders and multipliers, and a multiplexer. Reversible NAND/AND and NOR/OR gates are designed. A DKGP gate is used to design a reversible 1-bit full adder and 8-bit complementing adder. 4x4 and 8x8 multipliers are designed using compressors. A 2x1 multiplexer and 4x1 multiplexer are also designed using primitive gates. CMOS and SET implementations and their input/output waveforms are shown for the designed circuits.

![REFERENCES

73

[1] T. Esther Rani, M.A. Rani and R. Rao, “AREA optimized low power

arithmetic and logic unit,” IEEE International Conference on Electronics

Computer Technology, April 2011, pp. 224–228.

[2] Landauer. R., “Irreversibility and Heat Generation in the Computing

Process”, IBM J. Research and Development, vol. 3, pp. 183- 191, 1961.

[3] Bennett. C.H., “Logical reversibility of computation”, IBM Journal

Research and Development, volume 17, pp. 525-532, 1973.

[4] K. Uchida, K. Matsuzawa, J. Koga, R. Ohba, S. Takagi and A. Toriumi,

“Analytical Single-Electron Transistor (SET) Model for Design and Analysis of

Realistic SET Circuits,” Japanese Journal of Applied Physics, Vol. 39, No. 4B,

2000, pp. 2321-2324. doi:10.1143/JJAP.39.2321

[5] H. Inokawa and Y. Takahashi, “A Compact Analytical Model for Asymmetric

Single-Electron Tunneling Tran-sistors,” IEEE Transactions on Electron

Devices, Vol. 50, No. 2, 2003, pp. 455-461. doi:10.1109/TED.2002.808554

[6] S. Mahapatra, V. Vaish, C. Wasshuber, K. Banerjee and A. M. Ionescu,

“Analytical Modeling of Single Electron Transistor for Hybrid CMOS-SET

Analog IC Design,” IEEE Transactions on Electron Devices, Vol. 51, No. 11,

2004, pp. 1772-1782. doi:10.1109/TED.2004.837369](https://image.slidesharecdn.com/singleelctrontransistophase2-220711052226-35a508a5/85/Single-elctron-transisto-PHASE-2-pptx-61-320.jpg)

![74

[7]Dubuc. C., Beaumont. A., Beauvais. J. and Drouin. D., “Current

Conduction Models in the High Temperature Single-Electron Transistor,”

Solid-State lectronics, Vol.53, No. 5, pp. 478-482, 2009.

[9] Frans Willy and Yudi Darma ,” Modeling and simulation of single electron

transistor with master equation approach”, Journal of Physics:

Conference Series, Volume 739, Number 1,2016.

[10]Gangadhar Reddy Ramireddy “A Novel Power-Aware and High

Performance Full Adder Cell for Ultra low Power Design,” IEEE

International Conference on Circuit, Power and Computing Technologies,

2014, pp. 1121-1126.

[11]JVR Ravindra, Gangadhar Reddy Ramireddy and Harikrishna

Kamatham, “Design of Ultra Low Power Full Adder using Modified Branch

Based Logic Style,” IEEE European Modelling Symposium, 2013, pp.

691-696.

[12] Rajesh Parihar, Nidhi Tiwari, Aditya Mandloi and Dr.Binod Kumar, “An

Implementation of 1-Bit Low Power Full Adder Based on Multiplexer and

Pass Transistor Logic,” IEEE International Conference on Information

Communication and Embedded System, 2014, pp. 101- 103.

[13]L. Dhulipalla and A. Deepak, “Design and implementation Of 4-bit ALU

using FINFETS for nano scaletechnology,” IEEE International Conference

on Nanoscience, Engineering and Technology , November 2011, pp. 190–

195.](https://image.slidesharecdn.com/singleelctrontransistophase2-220711052226-35a508a5/85/Single-elctron-transisto-PHASE-2-pptx-62-320.jpg)

![75

[14] A. Srivastava and C. Srinivasan, “ALU Design Using Reconfigurable

CMOS Logic,” IEEE 45th midwest symposium on circuit and system, vol.

2, August 2002, pp. 663-6.

[15] Ravi Tiwari and Khemraj Deshmukh, “Design and analysis of low

power 11-transistor full adder,” IJAREEIE, vol. 3, issue 6, June 2014,pp.

10301-10307.

[16] Pooja Vaishnav and Mr.Vishal Moyal, “Performance Analysis Of 8-Bit

ALU For Power In 32 Nm Scale,” IJERT, vol. 1, issue 8, October 2012

pp. 1-3.

[17] S. Usha, M. Rajendren, A.Kavitha,”Low power area efficient ALU with

low power full adder”,IEEE conference on Computing for sustainable

global development,2016.

[18] Biswabandhu Jana, Anindya Jana, Subhramita Basak, Jamuna Kanta

Sing, Subir Kumar Sarkar,” Design and Performance Analysis of

Reversible Logic based ALU using Hybrid Single Electron

Transistor”,IEEE RAECS UIET Panjab University Chandigarh,2014.

[19] Anitesh Sharma, Ravi Tiwari,” Low Power 8-bit ALU Design Using Full

Adder and Multiplexer”, IEEE WiSPNET , 2016](https://image.slidesharecdn.com/singleelctrontransistophase2-220711052226-35a508a5/85/Single-elctron-transisto-PHASE-2-pptx-63-320.jpg)

![[20] Anindya Jana, N Basanta Sing, Jamuna K Sing and Subir Kumar Sarkar

,“Design and simulation of hybrid CMOS SET circuits”, Microelectronics

Reliability, Elseveier, Vol. 53, pp. 592-599, Issue 4, April 2013.

[21] Biswabandhu Jana, Anindya Jana, Jamuna Kanta Sing, and Subir

Kumar Sarkar, “A Comparative Performance Study of Hybrid SET-CMOS

Based Logic Circuits for the Estimation of Robustness” Journal of Nano

and Electronic Physics, Vol. 5 No. 3, pp. 54-57, 2013.

[23] Gouthami.P and RVS. Sathyanarayana, "Design of digital adder using

Reversible logic", International journal of engineering research and

applications,Vol 6, Issue 6, pp 53-57, 2016.

[24] Sarada. M and Muralidhar. M , "A novel design and implementation of

reversible adder cum subtractor", International journal of innovative in

engineering and technology, special issue on ETICE 16, pp 48-54, 2016.

[25] Y. Taur, D. A. Buchanan, W. Chen, D. Frank, K. Ismail, S. Lo, G.Sai-

Halasz, R. Viswanathan, H. Wann, S. Wind, and H. Wong, “CMOS

scaling into the nanometer regime,” Proc. IEEE, vol. 85, no. 4, pp. 486–

504, Apr. 1997

[26] K. K. Likharev, “Single-electron devices and their applications,”

Proc.IEEE, vol. 87, no. 4, pp. 606–632, Apr. 1999.

76](https://image.slidesharecdn.com/singleelctrontransistophase2-220711052226-35a508a5/85/Single-elctron-transisto-PHASE-2-pptx-64-320.jpg)

![77

[28] AnanthaLakshmi.A,V and Sudha.G.F, "An Efficient Implementation

of a Reversible Single Precision Floating Point Multiplier Using 4:3

Compressor", Elsevier, Proc. of Int. Conf. on Advances in

Information Technology and Mobile Communication, pp 229-238,

2013.

[29] Sagar, K Suresh Babu, " Design of Low Power Vedic Multiplier

Based on Reversible Logic", Int. Journal of Engineering Research

and Application ISSN : 2248-9622, Vol. 7, Issue 3, ( Part -2) , pp.73-

78, 2017.

[30] Nekkanti Gowthami and K. Srilakshmi, " Design and

mplementation of Reversible Multiplier using optimum TG Full

Adder". IOSR Journal of Electronics and Communication

Engineering (IOSR-JECE), Vol 12, Issue 3, Pp 81-89, 2017](https://image.slidesharecdn.com/singleelctrontransistophase2-220711052226-35a508a5/85/Single-elctron-transisto-PHASE-2-pptx-65-320.jpg)