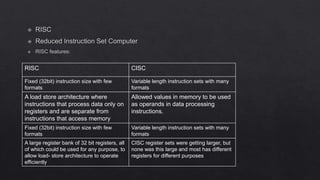

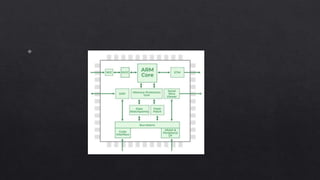

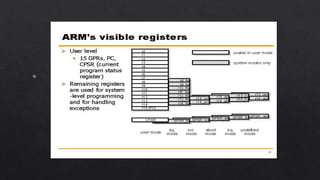

The document compares RISC and CISC architectures, highlighting RISC's fixed 32-bit instruction size and load-store design with a large register bank. In contrast, CISC features variable length instruction sets and larger but purpose-specific registers. Additionally, it discusses the differences in instruction decoding and execution efficiency between the two architectures.