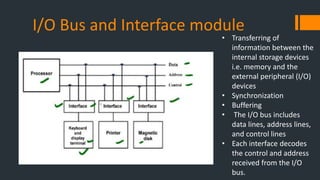

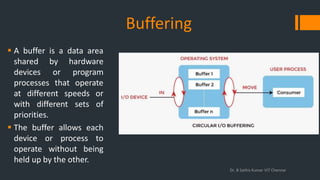

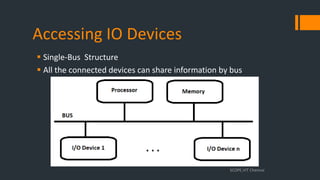

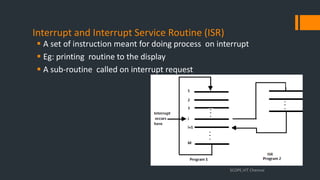

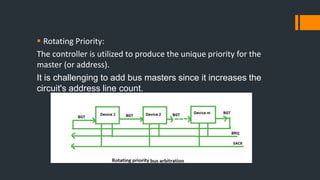

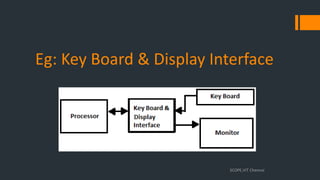

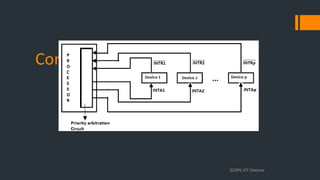

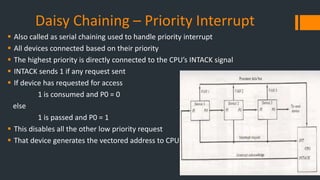

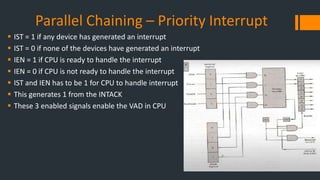

The document provides an overview of I/O interfacing and communication in computer systems, detailing the process of connecting various hardware components for effective data transfer. It explains concepts such as buffering, command types for interfaces, handshaking for communication setup, and methods for data transfer including programmed I/O, interrupt-initiated I/O, and direct memory access (DMA). Additionally, the document discusses bus arbitration methods, interrupt handling, and the importance of prioritization in managing multiple devices.