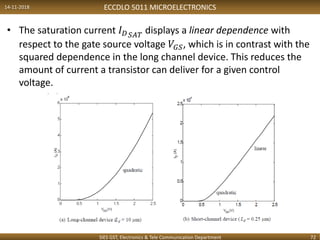

This document contains the syllabus, course outcomes, textbook information, and lecture slides for the ECCDLO 5011 MICROELECTRONICS course taught by Prof. Abhishek Ajit Kadam. The course aims to teach students about basic MOS transistor fabrication, MOS characteristics, integrated circuit biasing using MOSFETs, and designing active load amplifiers. The lectures cover topics such as MOSFET physics, I-V characteristics of MOSFETs in different regions of operation, and the history and development of microelectronics technology.

![ECCDLO 5011 MICROELECTRONICS

• Threshold Voltage

The semiconductor/oxide surface is inverted when VGS is greater than the

Threshold voltage (VTH). The threshold voltage VTH is given by

𝑉𝑇 = 𝑉𝑇𝐻0 + 𝛾( 2𝜙 𝐹 + 𝑉𝑆𝐵 − |2𝜙 𝐹|)

Where 𝑉𝑇𝐻0 = 𝜙 𝑀𝑆 + 2𝜙 𝐹 +

𝑄 𝑑𝑒𝑝

𝐶 𝑜𝑥

Where 𝜙 𝑀𝑆 is difference between work function of polysillicon gate and

substrate. It is given by

𝜙 𝐹 =

𝑘𝑇

𝑞

ln[

𝑁𝑠𝑢𝑏

𝑛𝑖

]

Where

𝑞 is charge on electron given by 𝑒 = 1.6 ∗ 10−19

𝑐𝑜𝑢𝑙𝑜𝑚𝑏𝑠

𝑁𝑠𝑢𝑏 is doping concentration

𝑄 𝑑𝑒𝑝 is Depletion region charge given by (4𝑒𝜖 𝑠𝑖 𝜙 𝐹 𝑁𝑠𝑢𝑏)

𝐶 𝑜𝑥 is oxide capacitance per unit area given by

𝜖 𝑠𝑖

𝑡 𝑜𝑥

𝛾 is called as Body coefficient given by

2𝑒𝜖 𝑠𝑖 𝑁 𝑠𝑢𝑏

𝐶 𝑜𝑥

14-11-2018

SIES GST, Electronics & Tele Communication Department 35](https://image.slidesharecdn.com/microelectronicslectureppts-181114110703/85/Microelectronics-Basics-35-320.jpg)