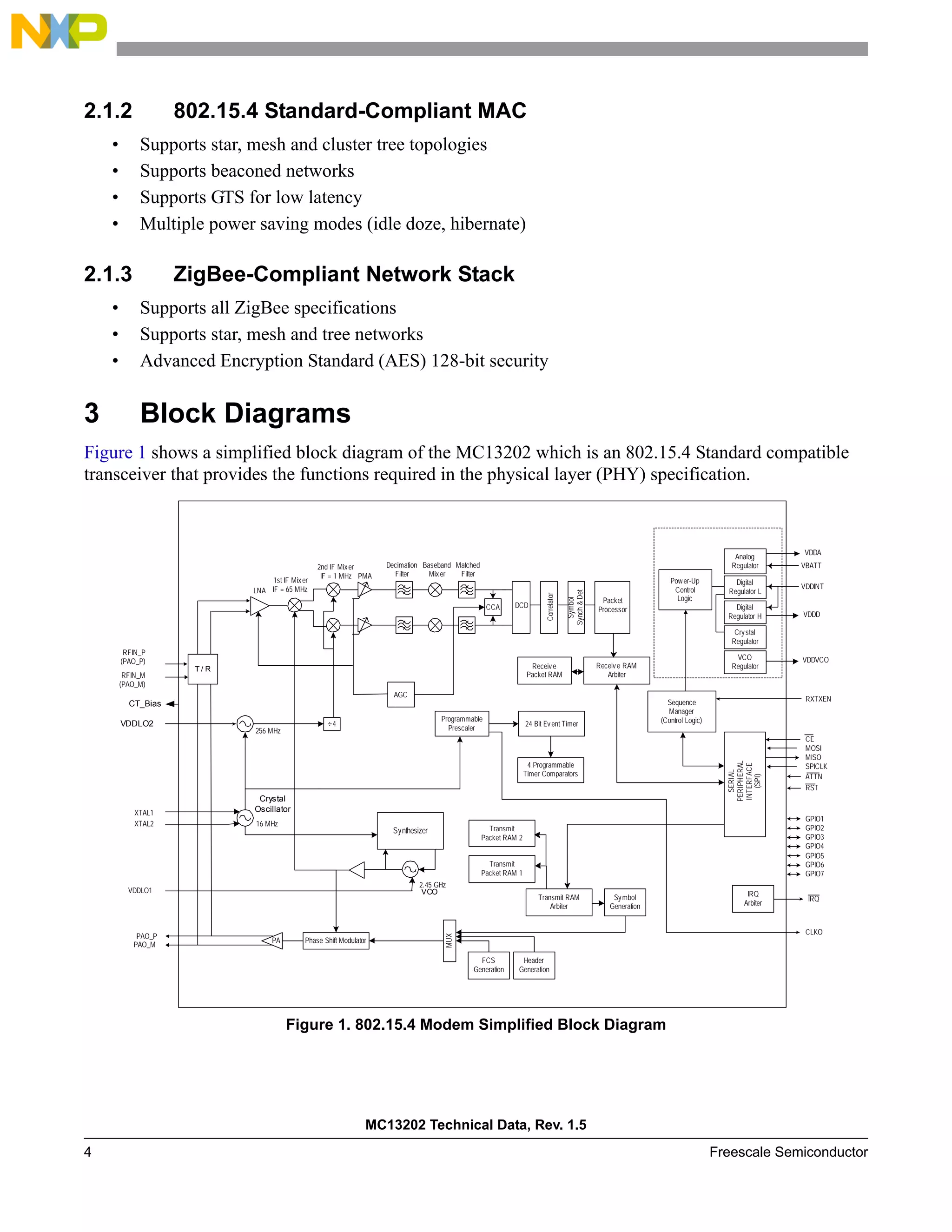

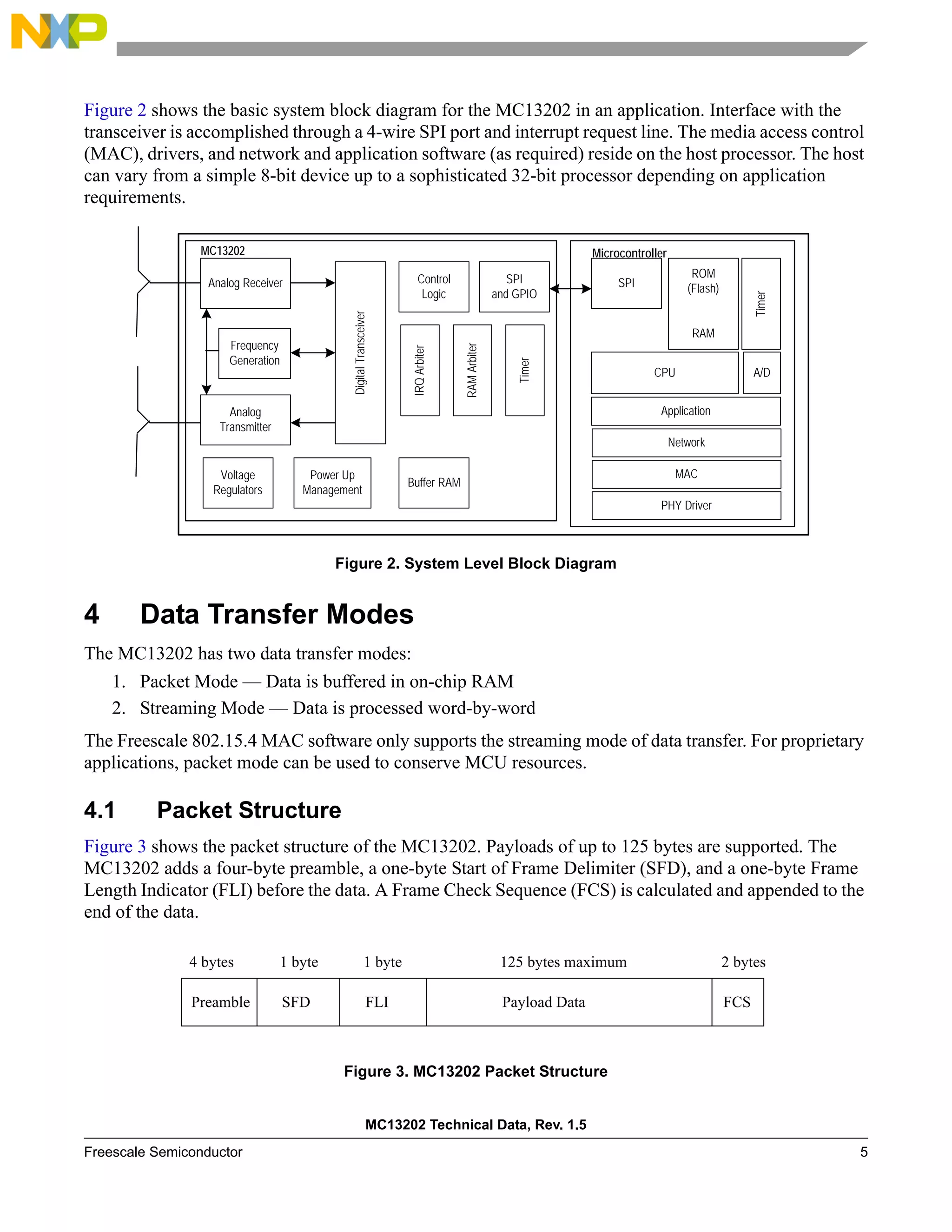

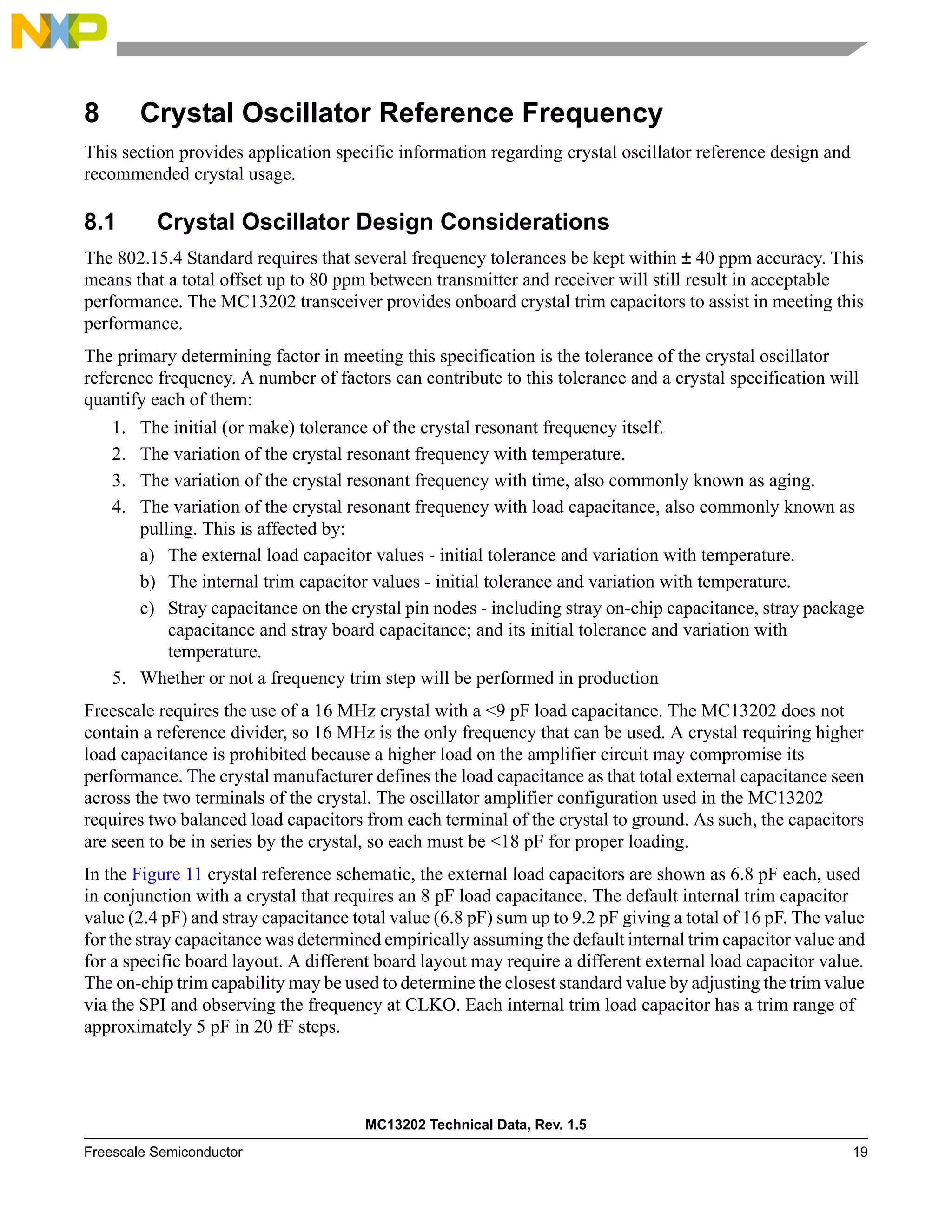

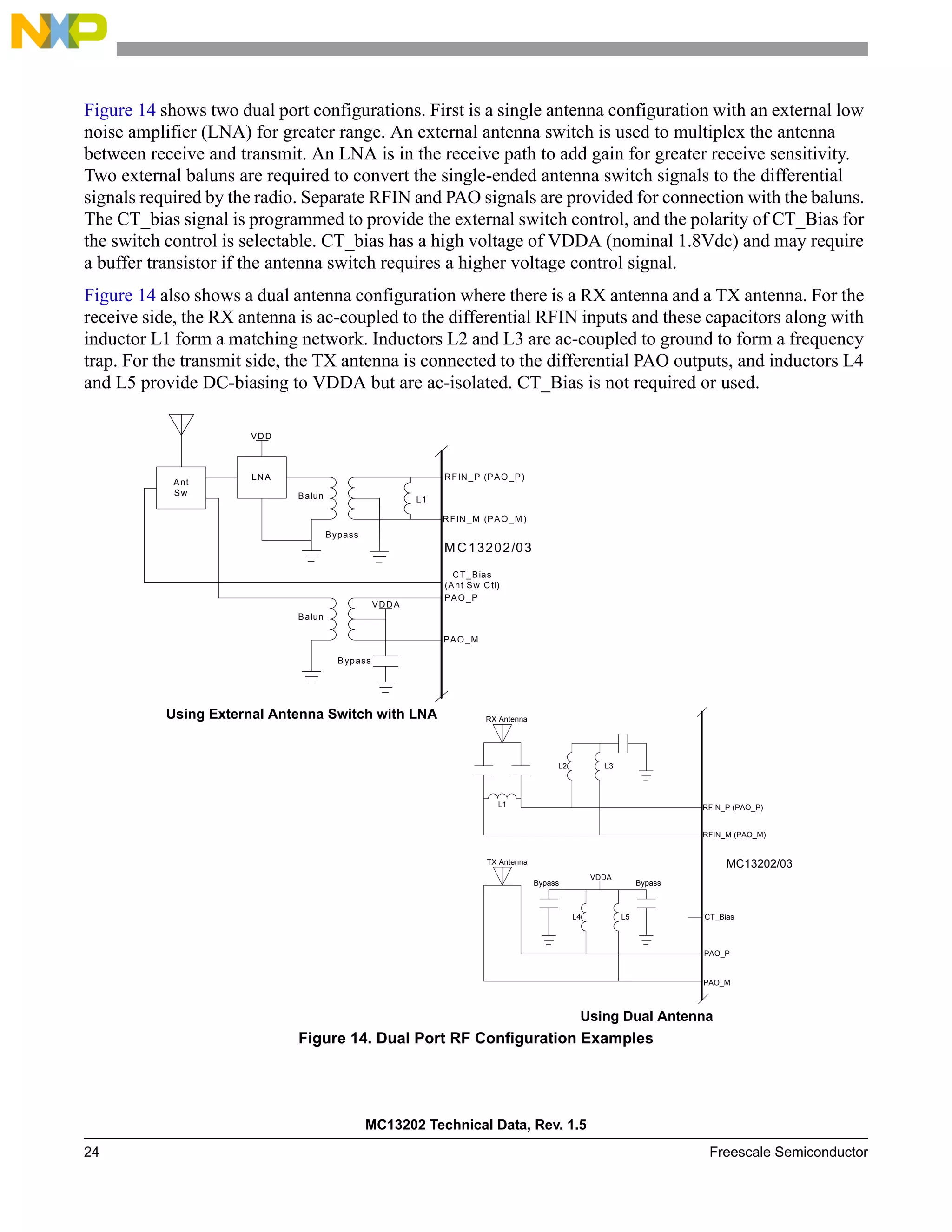

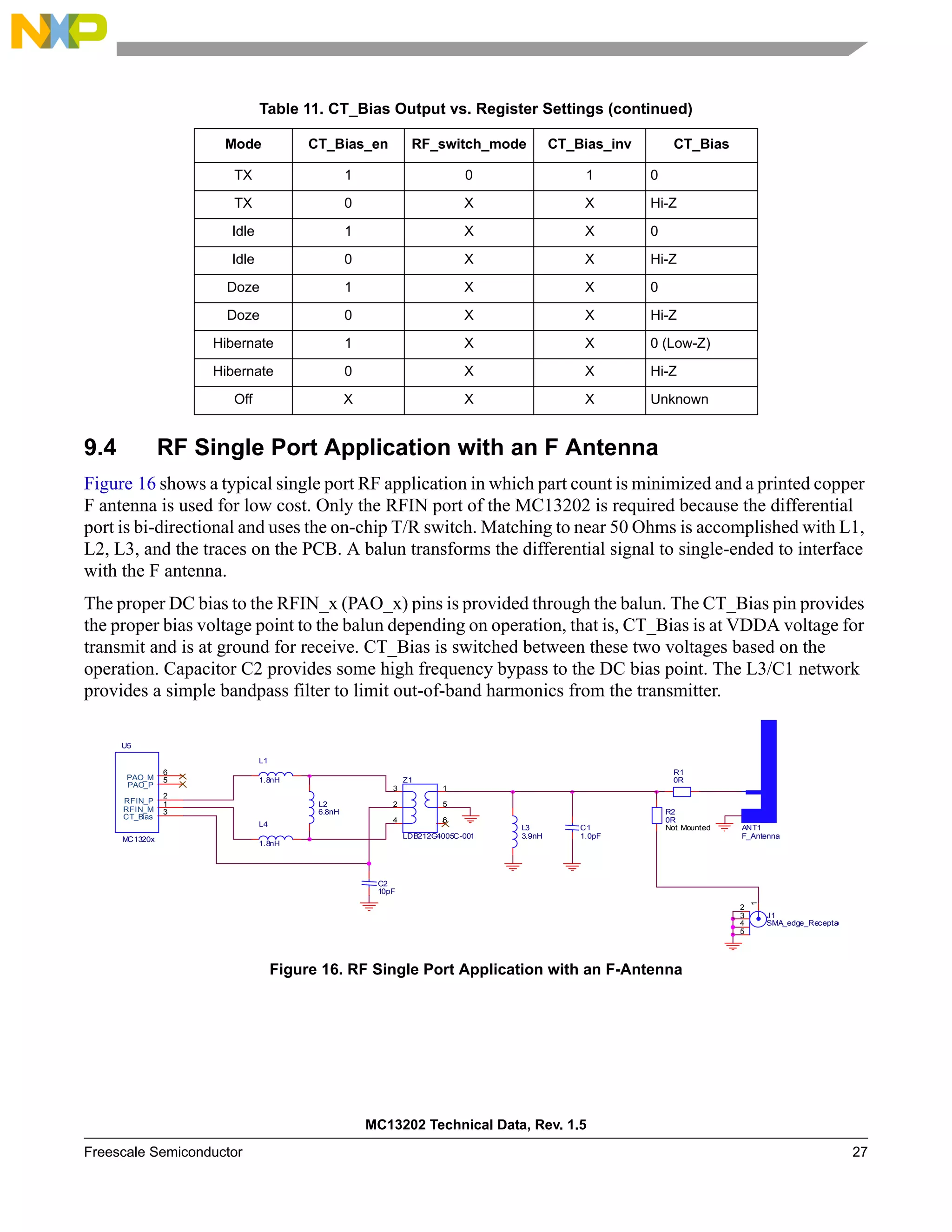

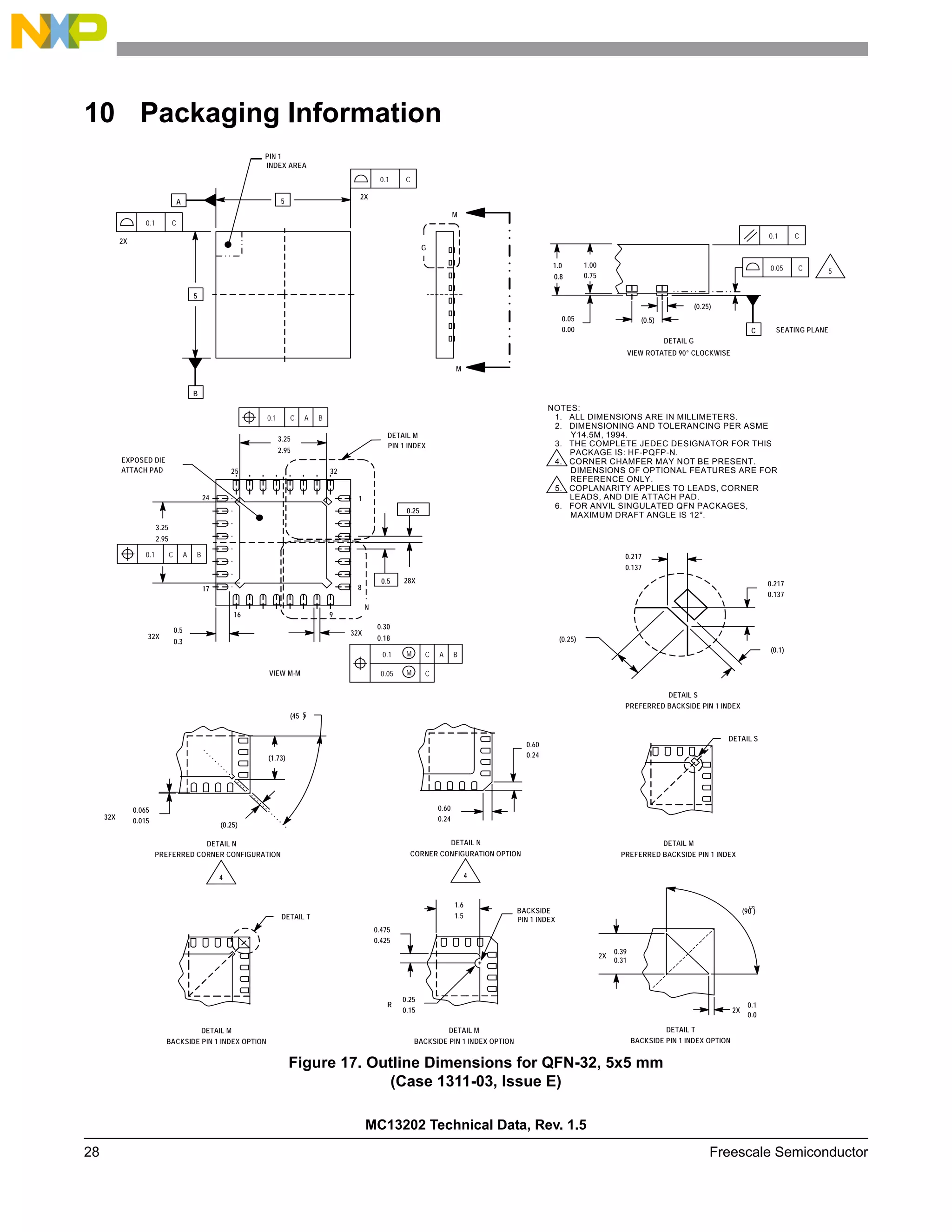

This document provides a summary of changes made in Revision 2 of the MC13202 datasheet from Freescale Semiconductor. The revision includes an addendum describing changes made to Revision 1.5, as well as the original Revision 1.5 datasheet. The addendum describes two changes: 1) a change to the case outline drawing for a new QFN-32 package, and 2) removal of references to case 1311-03. The full Revision 1.5 datasheet is then provided, describing the MC13202 low power transceiver chip.