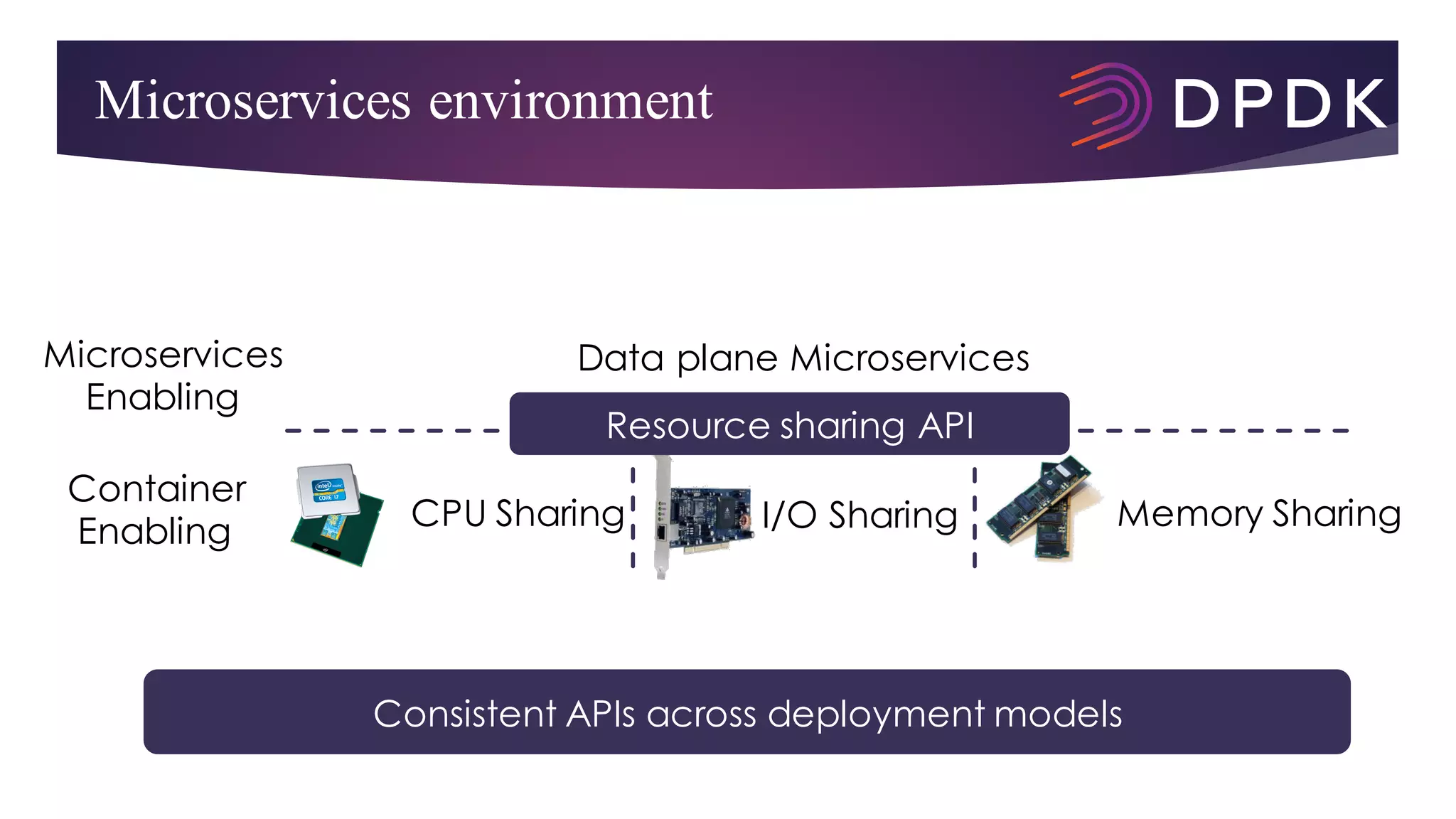

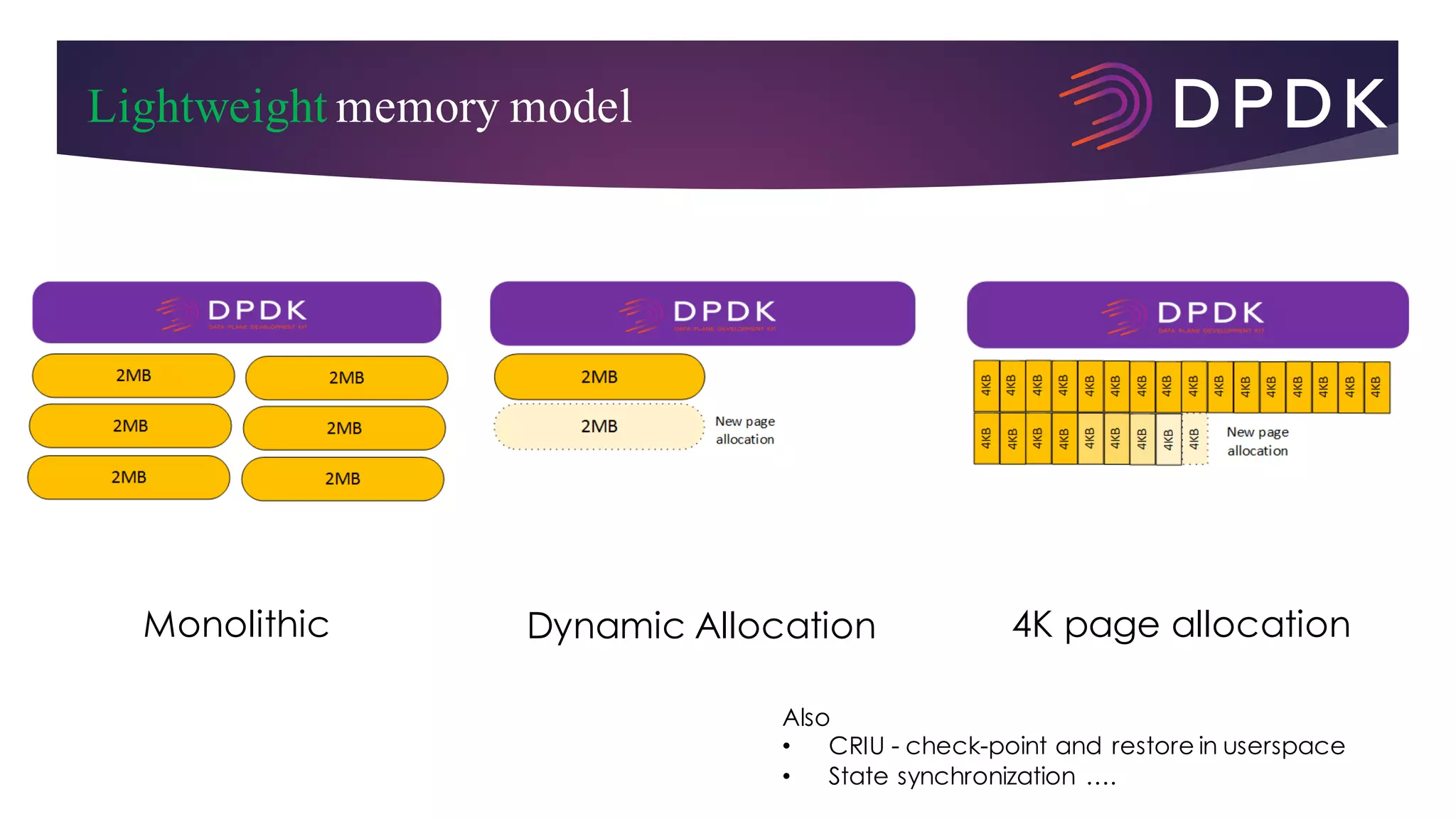

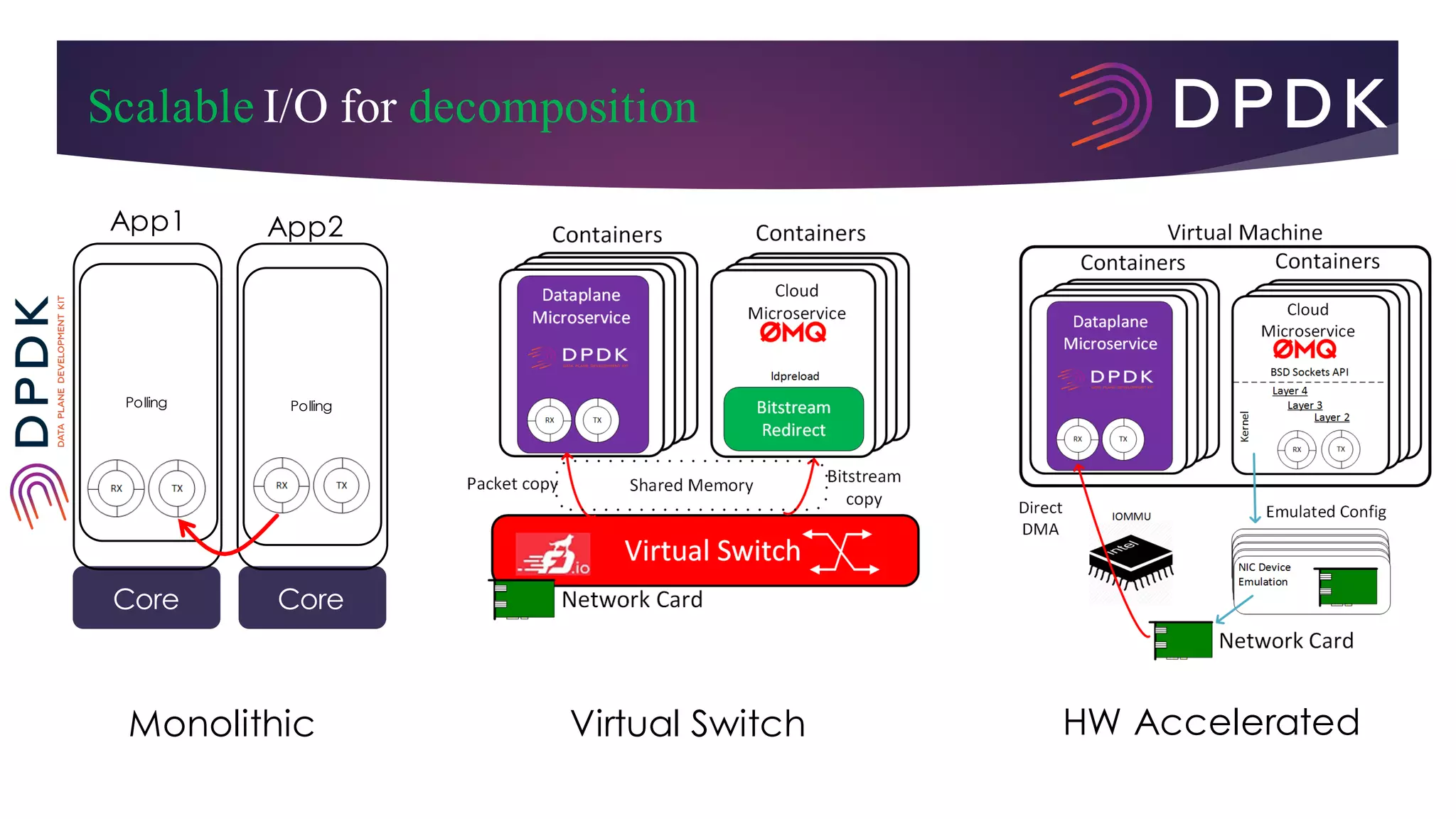

This document discusses the path to data plane microservices and provides an overview of microservices models. It describes the evolution from monolithic to in-process, multi-process, and multi-node microservices models. The key benefits of each model are high performance for in-process, multi-process scaling, and multi-node scaling. It also covers scheduling, memory, transport, failure protection, and live migration capabilities between the different models. Legal disclaimers are also provided at the beginning regarding performance testing and cost savings scenarios.