The document provides information on the L6238 sensorless spindle motor controller integrated circuit. Key features include:

- Sensorless commutation and speed control of a 3-phase brushless DC spindle motor.

- Integrated start-up and synchronization algorithms for spin-up and multi-drive arrays.

- Digital PLL for high accuracy speed control and locking to a reference frequency.

- Protection features and programmable functions for efficiency and noise reduction.

- Master/slave synchronization capability and bidirectional serial communication interface.

![a)the spindle is stopped.

b)the system is still running at a speed that

allows for resynchronization.

In order to minimize the ramp up time, the micro-

controller has the possibility to:

check the SPIN SENSE pin, (which toggles at

the Bemf zero crossing frequency)

enable the power to the motor based on the

previous information. Otherwise the uP may is-

sue a Brake command, followed by the start-

up procedure after the motor has stopped spin-

ning.

Brake

W/Mask

Hold & wait

for decision

Tri-state

W/Mask

Tri-state

W/Mask

RunBrk = 1

OutEna = 0

RunBrk = 1

OutEna = 1

OutEna = 1

&

RunBrk = 0

Run

W/Mask

Hold for

”Align & Go”

RunBrk

=

0

OutEna

=

0

Power

on

Reset

OutEna

=

1

RunBrk

=

1

RunBrk

=

0

RunBrk = 0

OutEna = 0

SeqInc = X

R

u

n

B

r

a

k

e

=

1

R

u

n

B

r

a

k

e

=

0

Run

Wo/Mask

SeqInc = 0

SeqInc = 1

SeqInc = 0

SeqInc = 1

Action across

line increments

sequencer

Auto Start-up

Enabled Disabled

RunBrk = 1

OutEna = 0

RunBrk = 1

OutEna = 1

O

u

t

E

n

a

=

0

O

u

t

E

n

a

=

1

Hold for

”Align & Go”

Start

”Align & Go”

Align =

Seqncr.

[Align

to

Phase

#

1]

StkRtr

=

0

[Align

to

Phase

#

3]

O

u

t

E

n

a

=

0

O

u

t

E

n

a

=

0

O

u

t

E

n

a

=

0

Align =

0

G

o =

0

Align

=

1

RunBrk

=

1

From Anywhere

Hold

for

”Resync”

Start

”Resync”

Resync = 1

Release

min mask

Run

G

o =

1

(Get

1st

Zc)

Zc

Reset

=

RunBrk = 1

OutEna = 0

O

u

t

E

n

a

=

0

O

u

t

E

n

a

=

0

O

u

t

E

n

a

=

0

No Zc

No Zc

Auto/Ext = 0

Stuck

Rotor

(hold)

(G

et 2

nd Z

c)

Zc R

eset=

OutEna = 1

&

RunBrk = 1

StrRtr = 0

StrRtr = 0

Mono

=

0

RunBrk = 0

&

OutEna = 0

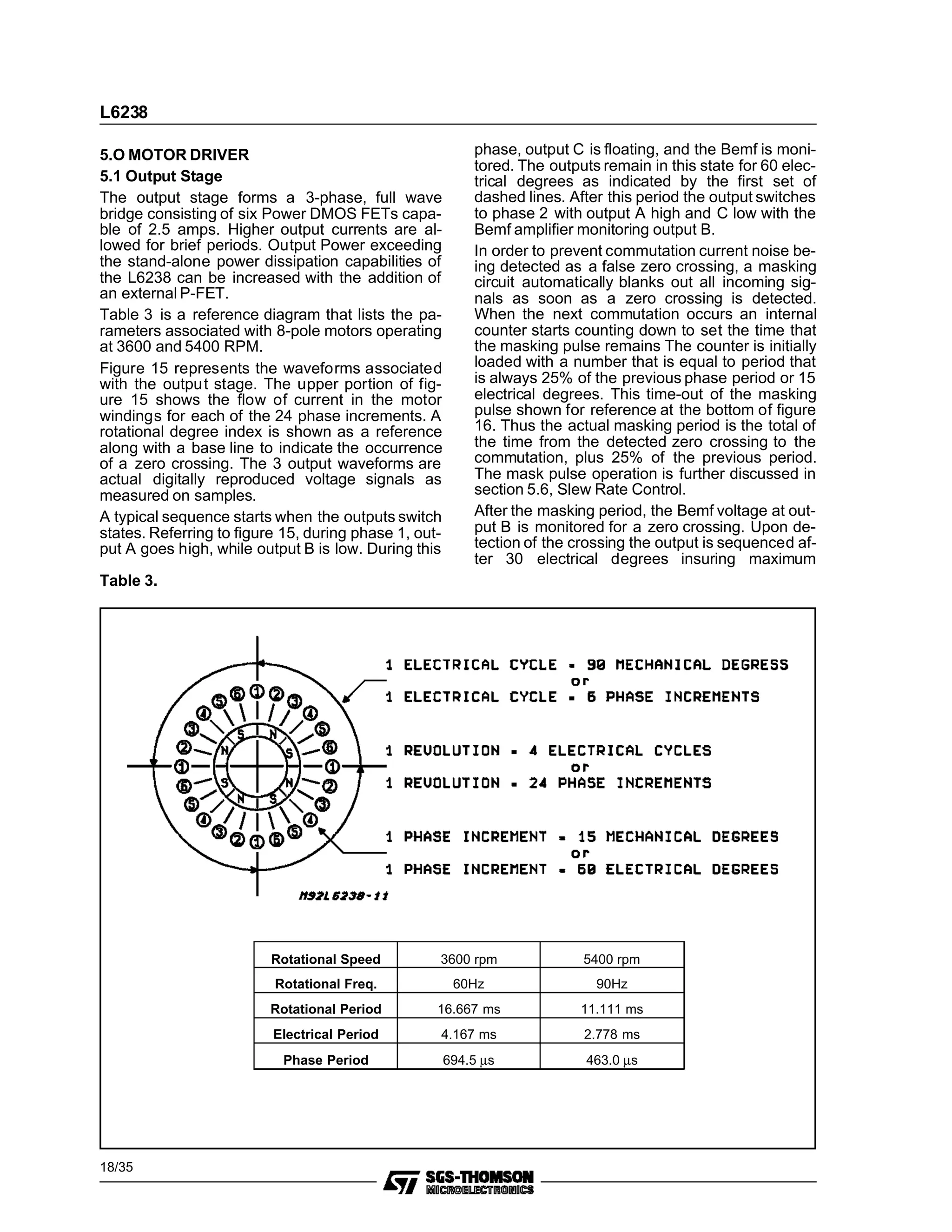

Figure 4: State Diagram

L6238

8/35](https://image.slidesharecdn.com/l62831-230514150940-a716bb15/75/L6283-1-3-pdf-8-2048.jpg)

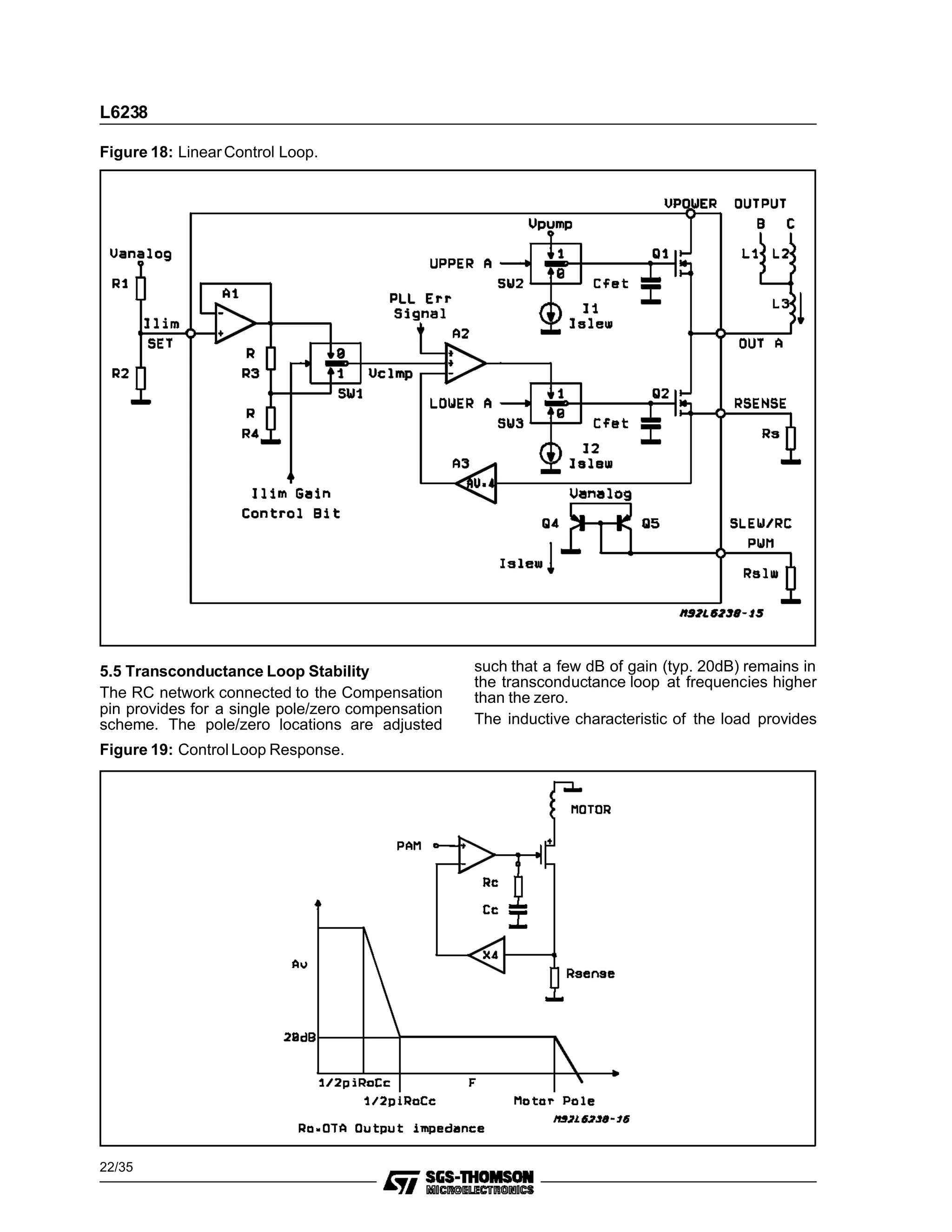

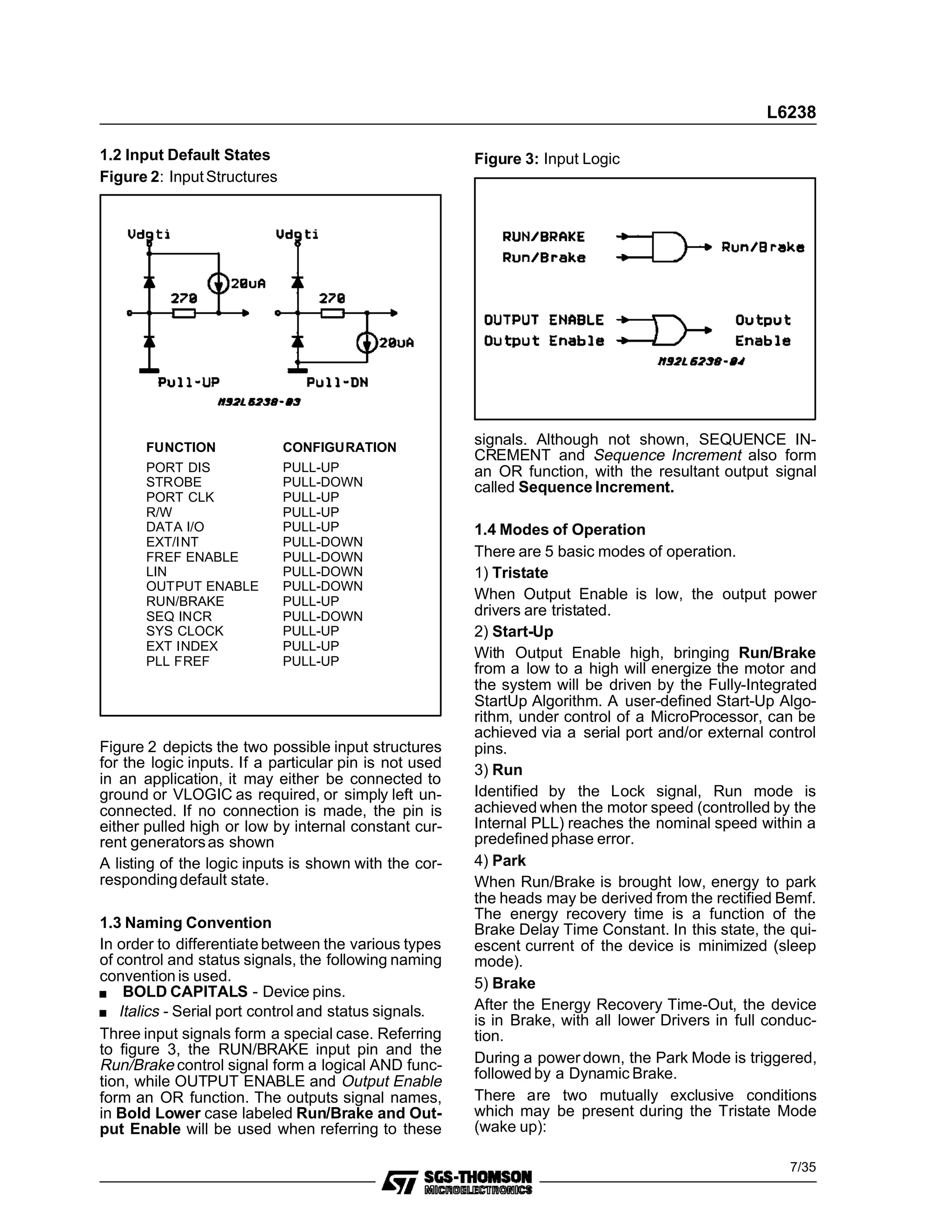

![2.0 STATE DIAGRAMS

2.1 State Diagram

Figure 4 is a complete State Diagram of the con-

troller depicting the operational flow as a function

of the control pins and motor status. The flow can

be separatedinto four distinct operations.

2.2 Align + Go

Figure 5 represent the normal flow that will

achieve a spin-up and phase lock of the spindle

motor. Upon power up, the controller first checks

to determine if the motor is still spinning. This

”Hold For Resync” decision block will be dis-

cussed later.

Hold & wait

for decision

RunBrk = 0

RunBrk = 1

Hold for

”Align & Go”

Hold

for

”Resync”

Start

”Align & Go”

Align =

Seqncr.

Run

[Align

to

Phase

#

1]

Go

=

1

[Align

to

Phase

#

3]

O

u

t

E

n

a

=

0

O

u

t

E

n

a

=

0

O

u

t

E

n

a

=

0

Align =

0

Go =

0

Power

on

Reset

Align

=

1

RunBrk

=

1

OutEna

=

1

OutEna

=

0

RunBrk = 1

OutEna = 0

OutEna = 0

&

RunBrk = 0

Figure 5: Align+Go

L6238

9/35](https://image.slidesharecdn.com/l62831-230514150940-a716bb15/75/L6283-1-3-pdf-9-2048.jpg)