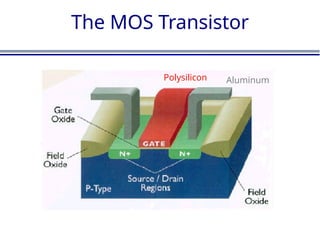

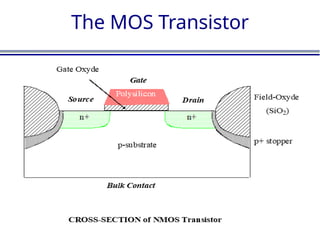

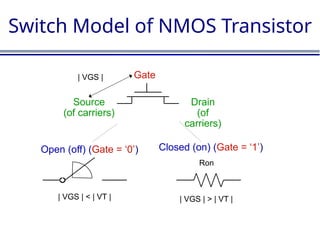

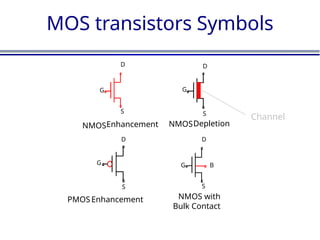

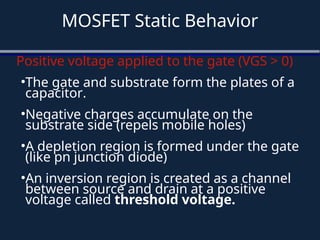

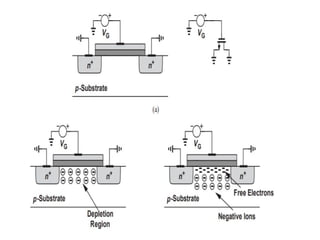

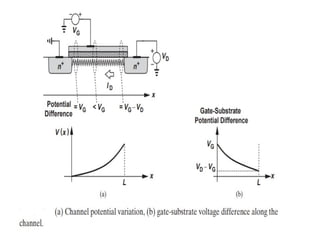

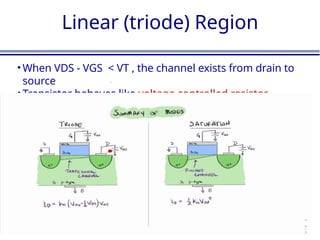

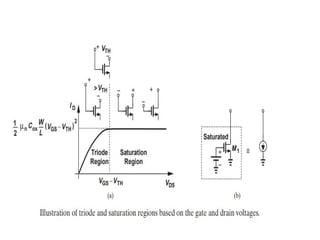

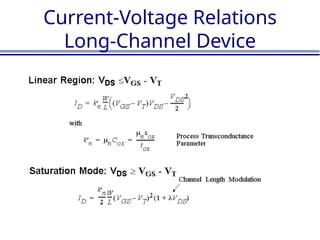

The document discusses the structure and operation of MOS transistors, detailing their I-V characteristics in both the triode and saturation regions. It covers key concepts including threshold voltage, drain current calculations, and the functioning of NMOS and PMOS transistors. The summary includes the behavior of these devices under various voltage conditions and their representation as switches.