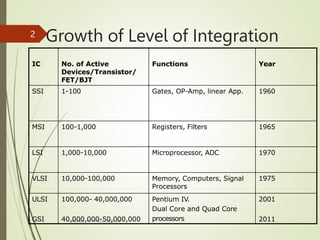

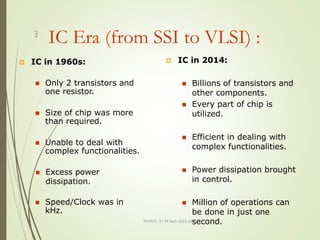

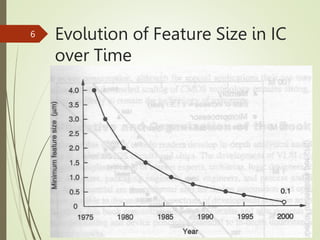

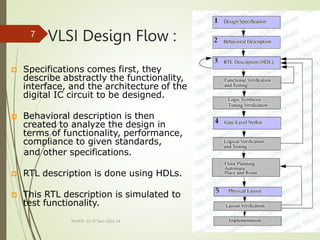

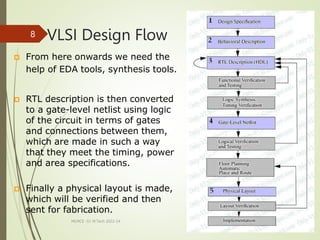

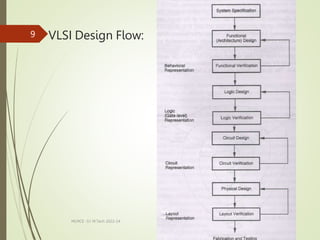

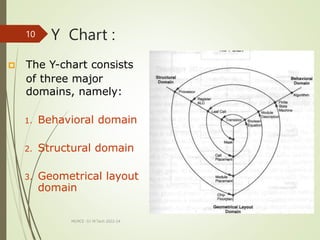

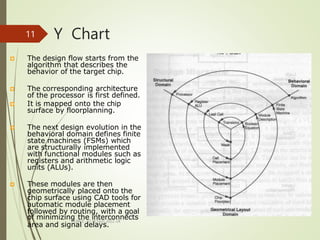

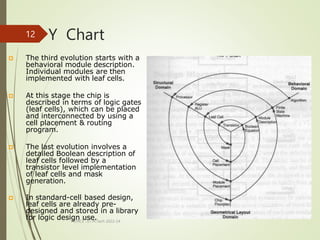

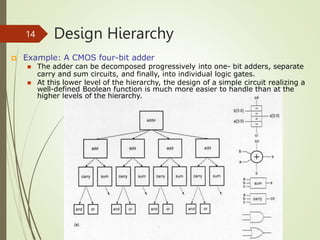

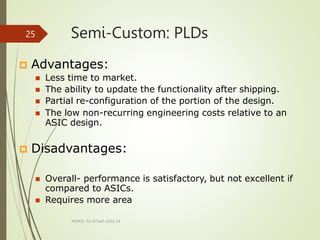

The document provides an overview of CMOS VLSI design, covering its historical development, the evolution of integrated circuit complexities, and essential design methodologies and concepts like hierarchy, modularity, and locality. It outlines the progression from early simple circuits to modern high-performance chips under Moore's Law and describes various design flows and methodologies including full custom, semi-custom, and programmable logic devices. Key concepts such as regularity in design, the importance of interfaces, and using hierarchical techniques to manage complexity in VLSI design are emphasized.