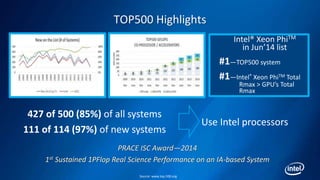

- Intel dominates the TOP500 supercomputer list, powering 427 of the top 500 systems and 111 of the newest systems using Intel Xeon and Xeon Phi processors.

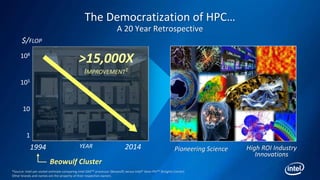

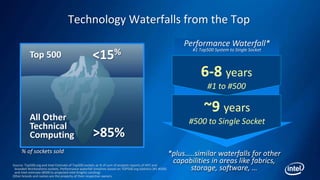

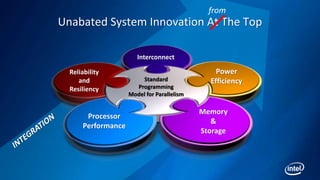

- HPC performance has improved over 15,000x in the past 20 years, with innovations like clusters now enabling top performance to waterfall down to single-socket systems within 6-8 years.

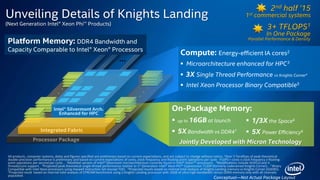

- Knights Landing, the next generation Intel Xeon Phi product, will provide over 3 teraflops of performance in a single package in 2015, using enhanced Intel Atom cores and on-package memory.