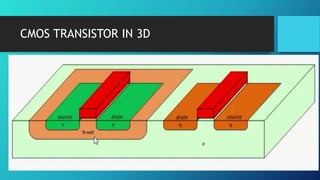

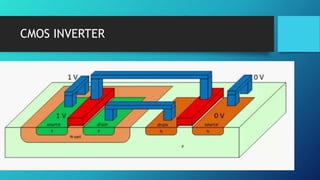

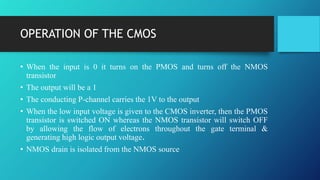

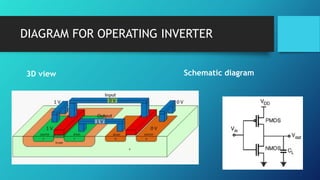

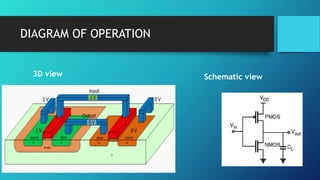

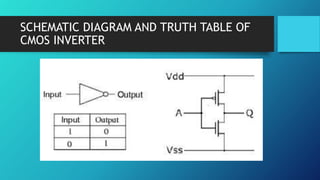

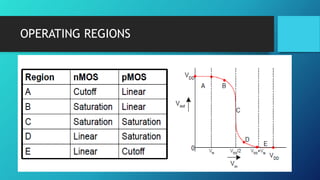

The document discusses the CMOS inverter, which is a basic building block used in digital circuits. It consists of a PMOS transistor and an NMOS transistor connected together. When the input is low, the PMOS turns on and the NMOS turns off, causing the output to be high. When the input is high, the PMOS turns off and the NMOS turns on, causing the output to be low. CMOS inverters are widely used in electronic devices due to their low power consumption.