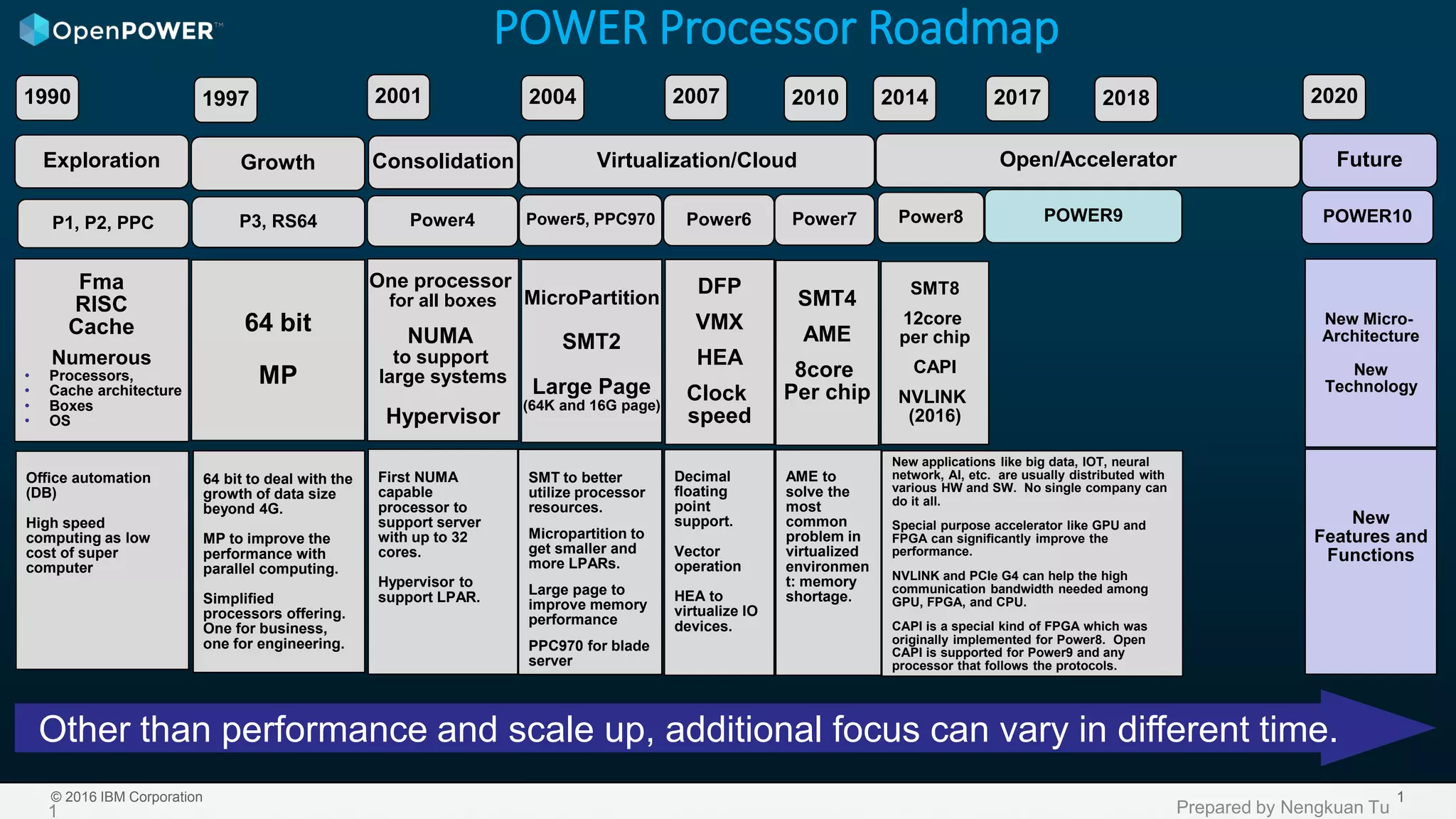

This document summarizes the Power processor roadmap from 1990 to 2020. It discusses key technologies and features introduced at each step like 64-bit support, multi-processing, simplified processor offerings, NUMA, hypervisor support, and larger page sizes. It notes how the focus has evolved from performance and scale to virtualization and cloud computing. It outlines new directions for Power10 like support for emerging workloads in big data, IoT, AI through technologies like accelerators, GPUs, and high-speed interconnects between components.