This document describes an assignment involving designing a system to send data from one PIC16F877A microcontroller to another using a FIFO. It detects single bit errors using parity check, and has the receiver send a retransmit command when an error is detected, increasing the error count. A bit error injector was used to test the system by increasing the probability of errors. The document includes wiring diagrams, flow charts of the noise injection, transmitter and receiver processes, a test plan and procedure, and considerations of the design.

![______________________________________________________________________________

-8 of 19-

Start

u32 randonCounter = 0

u16 prob[11] = [values…..]

If(TMR2IF == True)

Ra4 = 1 (Remove bit error)

milliSecondCounter++

randonCounter++

If (randomCounter == 500)

RA5 = !RA5

randomCounter = 0

if(myRandomNumber >

prob[value])

errorCount++

RA4 = 0

TMR2IF = False

If(INTF == True)

If (clockwise)

If (value == TOP_LIMIT)

Value = 0

Value++ If(value == 0)

Value--

Value = TOP_LIMIT

IMTF = False

End

Return

myInterruptFunction()

Y

Y

Y

Y

Y Y

N

N

N

N

N

Y

N](https://image.slidesharecdn.com/5b2dd77b-d037-4c14-8812-2713f858453e-170112194854/85/Emeto_Chukwuemeka_7691553_A8-8-320.jpg)

![______________________________________________________________________________

-9 of 19-

Start

U32 secoundsCounter = 0

u8 seed = 0

char string1[20]

portInit()

LCDInit()

ATDInit()

seed = getADC()

srand(seed)

timer2Init()

While(1)

myRandomNumber = rand()

if(milliSecondsCounter >= 1000)

secondsCounter++

milliSecondsCounter = 0

sprintf(string1, "T:%lu P:%u%%",secondsCounter, 10*value)

clearDisplay()

setDisplayLine(1, 0)

writeString(string1)

sprintf(string1, "E:%lu", errorCount)

setDisplayLine(2, 0)

writeString(string1)

End

Main

Y

Y

N](https://image.slidesharecdn.com/5b2dd77b-d037-4c14-8812-2713f858453e-170112194854/85/Emeto_Chukwuemeka_7691553_A8-9-320.jpg)

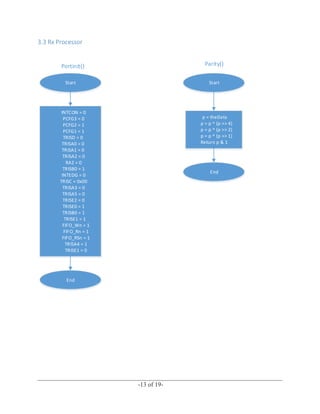

![______________________________________________________________________________

-12 of 19-

Start

If INTF == 1

FIFO_Wn = 0;

FIFO_Rn = 1;

While (FIFO_NOT_FULL)

FIFO_D = i++

calcparity = Call function [Parity(FIFO_D)]

RA4 = calcparity;

FIFO_Wn = 0;

FIFO_Wn = 1

count++;

INTF = 0

If TMR2IF == 1

oneSecondCounter++

TMR2IF = 0

End

Y

Y

Y

N

N

N

myISR()

Start

portInit()

LCDInit()

FIFOReset()

timer2Init()

setDisplayLine(1, 0)

writeString("Throughput=")

setDisplayLine(2, 0)

writeString("RTnumber =");

Enable Interrupts

INTF = 0

TMR2IF = 0

INTE = 1

TMR2IE = 1

PEIE = 1

GIE = 1

delay(200)

INTF = 1;

While(1)

If (RE1 ==1)

retrans++

FIFOReset()

INTF = 1

If (oneSecondCounter == 19

ltoa(myNum, count, 10)

setDisplayLine(1, 11)

writeString(myNum)

ltoa(myNum, retrans, 10)

setDisplayLine(2, 11)

writeString(myNum)

prevCount = count

count = 0

oneSecondCounter = 0

End

Y

Y

N

N

main](https://image.slidesharecdn.com/5b2dd77b-d037-4c14-8812-2713f858453e-170112194854/85/Emeto_Chukwuemeka_7691553_A8-12-320.jpg)

![______________________________________________________________________________

-19 of 19-

7. The throughput compromises for no noise by sending bigger packets than it did previously and

this is how it is maximized. The throughput is optimized by sending smaller packets when there

is no noise. One factor affecting the different times is adjusting the clock cycle of the micro

controller, this will definitely increase or decrease the packet transmission time depending on

how the clock cycle is being adjusted. The throughput will definitely take longer to send the

smaller packets than the bigger ones because there are more smaller packets than they are bigger

ones. Getting an error will also increase the time it takes for transmission. A size of a packet

should be 256 and should have a 9-bit word. The packet size is also shorter when the noise level

increases because there are more errors and this causes lesser packet size. The packet size is

longer when the noise level decreases because there are less errors and therefore more good

packets.

7 Conclusion

After successfully building the required sender, receiver and bit injector error circuit with each

respective LCD, writing the code for the sender and receiver and using the given code for the bit

injector error circuit, debugging the code and finally implementing and running the code through

the MPLAB X IDE, the receiver circuit successfully received its respective information from the

sender and they both had the same throughput value which was one requirement of the project,

the receiver also detected errors from the bit injector when the probability was increased which

was another requirement of the project, a retransmit signal was sent from the receiver to the

sender each time the receiver received a bad byte, also another requirement of the project, and

finally, increasing the error probability increased the error count and the number of signals being

retransmitted while taking the error probability stopped the retransmit signal and the error count.

Therefore, all the requirements for the project were met.

References

[1].W. Kinsner, ECE4240 Microprocessor Interfacing For Real Time Systems, Final Lab Report

Guide (2014)

[2]. W. Kinsner, ECE3730 PRINCIPLES OF EMBEDDED SYSTEMS DESIGN, Project 4

manual, Dual-Microcontroller FIFO Data Transfer with Emulated Random Noise Injected into

the Data Channel, ECE3730Project4Mv311.pdf](https://image.slidesharecdn.com/5b2dd77b-d037-4c14-8812-2713f858453e-170112194854/85/Emeto_Chukwuemeka_7691553_A8-19-320.jpg)