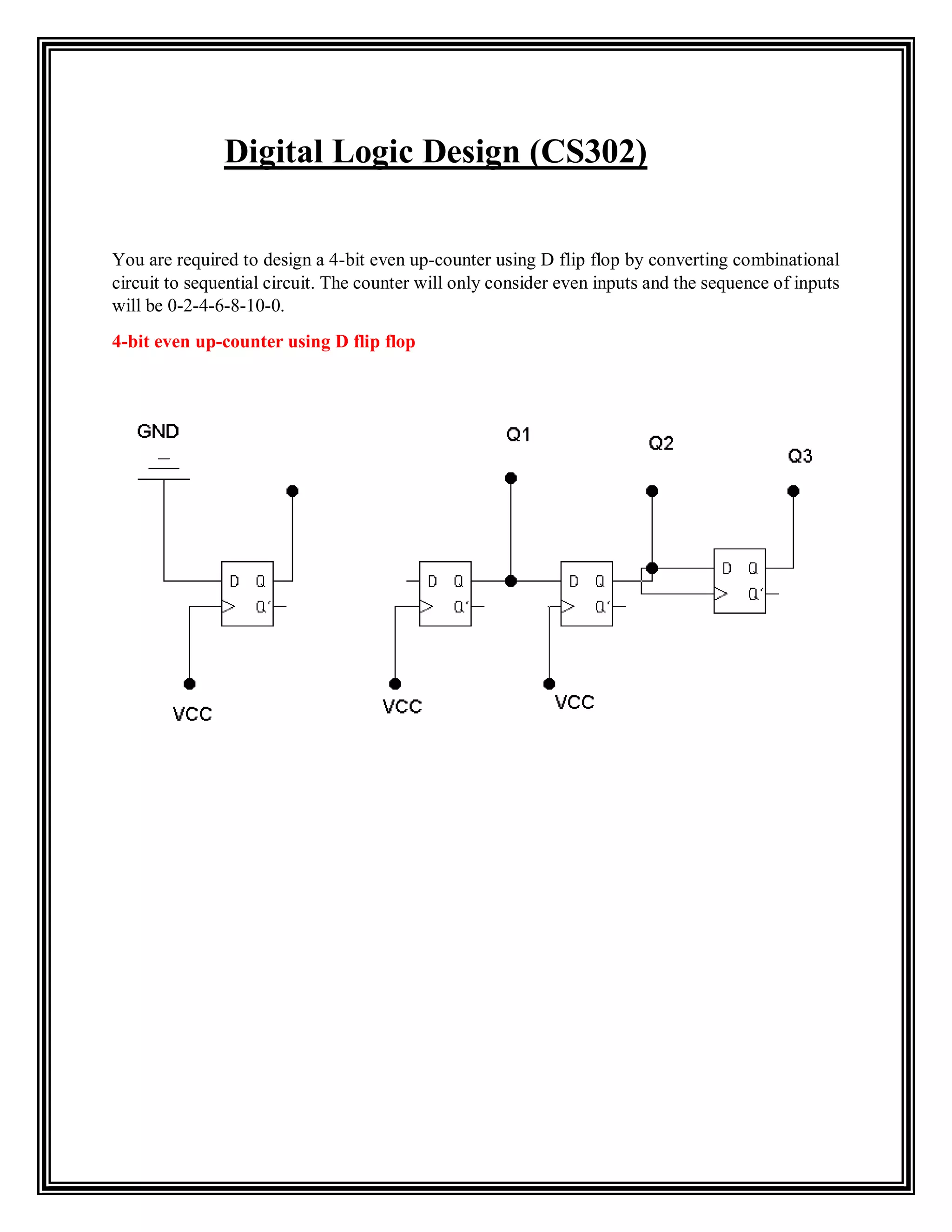

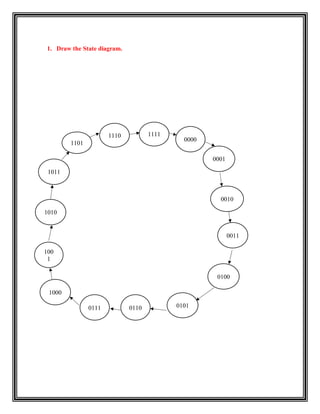

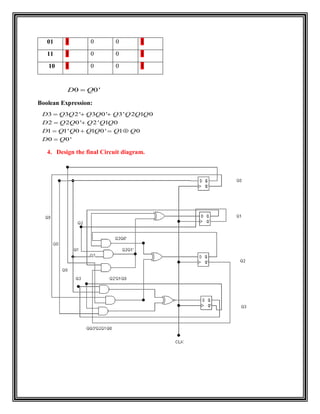

The document outlines the design of a 4-bit even up-counter using D flip-flops, focusing on a sequence that only includes even numbers. It specifies the steps to create a state diagram, generate a state transition table, derive simplified boolean expressions, and design the final circuit diagram. The main outputs include the state and transition details for proper implementation of the counter.