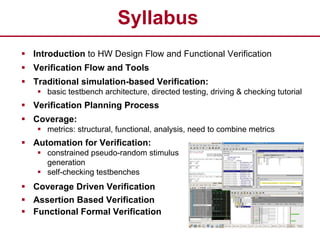

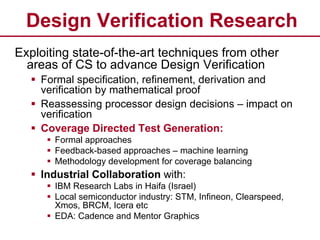

The document provides information on the COMSM0115 Design Verification course which aims to familiarize students with routine design verification tasks and techniques, covering topics like simulation-based verification, coverage metrics, formal verification, and outlines opportunities for undergraduate and graduate student projects and research collaboration with industry partners.