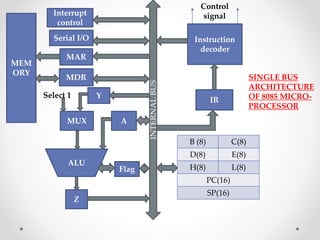

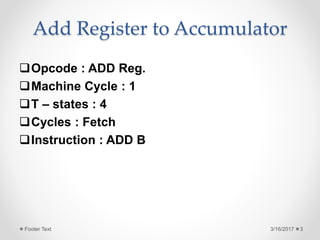

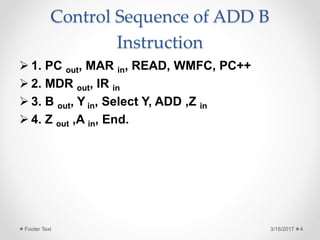

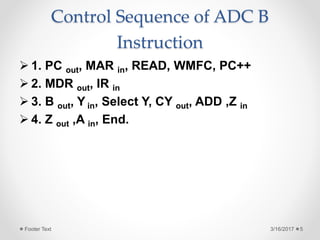

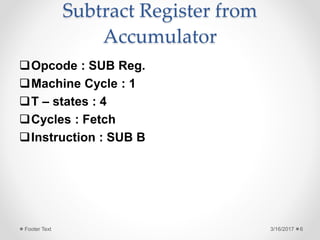

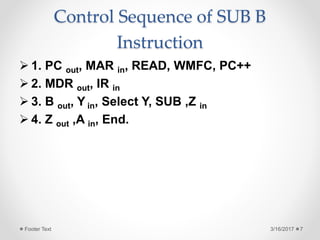

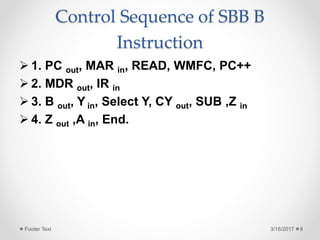

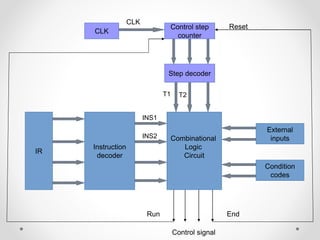

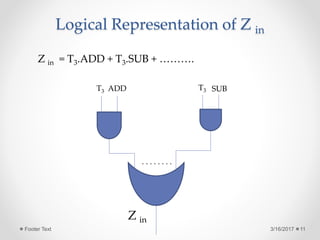

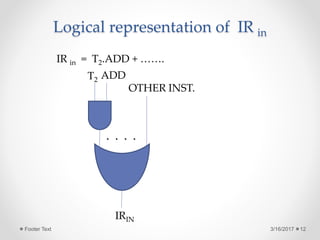

This document discusses the control sequences and hardwire approach for the 8085 microprocessor. It provides the control sequences for ADD B, ADC B, SUB B, and SBB B instructions. Each control sequence lists the steps involved including fetching the instruction and operands and performing the arithmetic operation. It also discusses the hardwired control unit organization that uses a control step counter, step decoder, and combinational logic circuit to generate control signals in the proper sequence to execute instructions. The control signals are represented logically based on the instruction and timing.