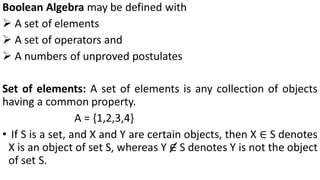

- The document discusses Boolean algebra and its properties.

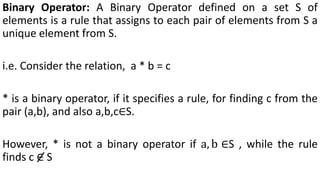

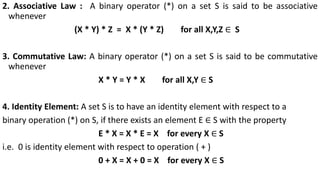

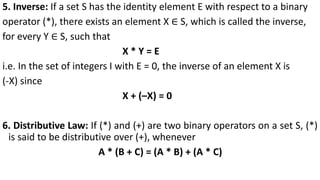

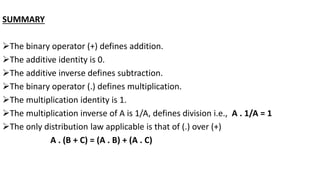

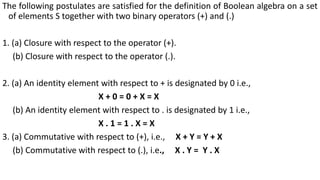

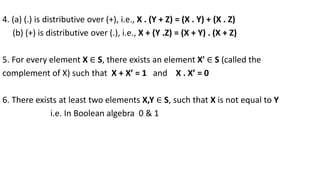

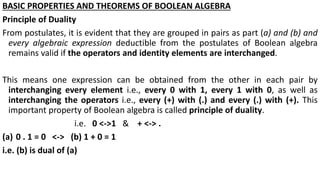

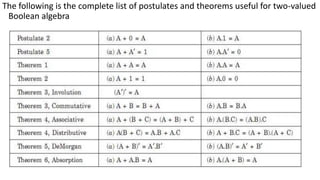

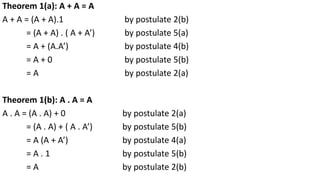

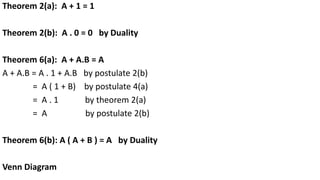

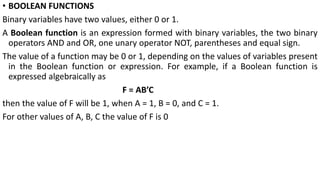

- Boolean algebra defines binary operators for logical operations like AND (.) and OR (+). It also defines identities and inverses.

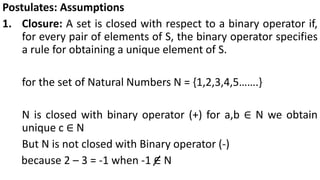

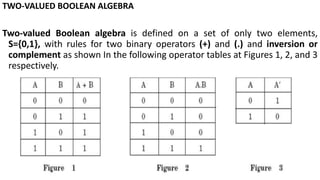

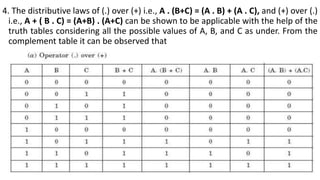

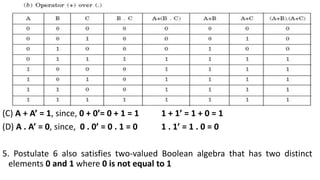

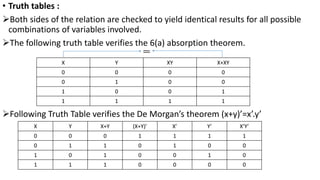

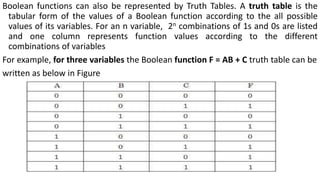

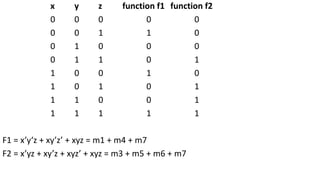

- The algebra can be represented by truth tables to show it obeys properties like closure, identity, inverse, commutative, associative, and distributive laws.

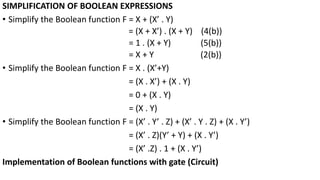

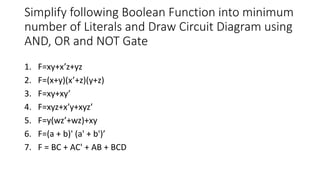

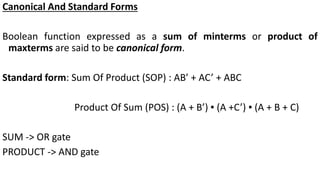

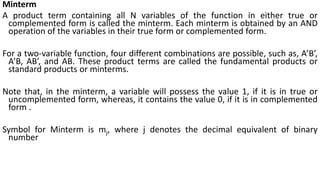

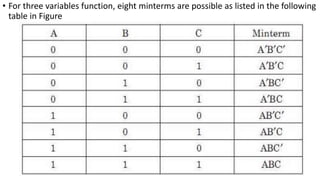

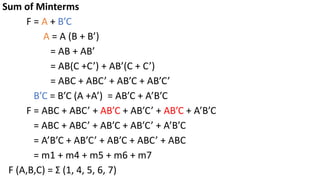

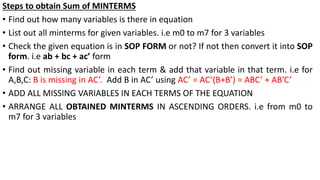

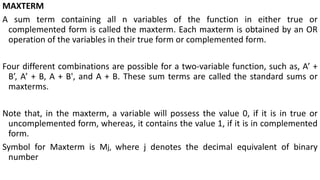

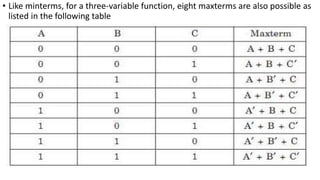

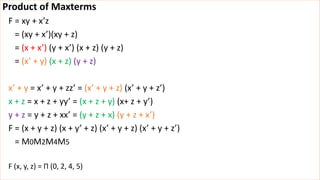

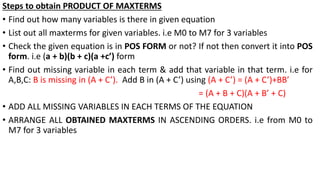

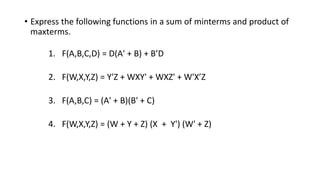

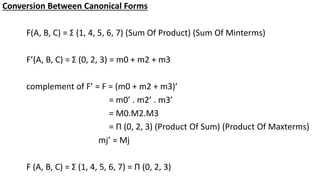

- Boolean functions and expressions can be simplified, converted to canonical and standard forms using sums of minterms and products of maxterms.