Tnkts p2

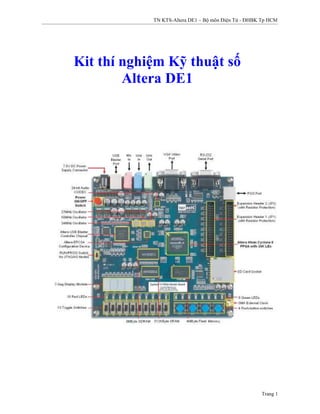

- 1. Trang 1 TN KTS-Altera DE1 – B môn i n T - HBK Tp HCM Kit thí nghi m K thu t s Altera DE1

- 2. Trang 2 TN KTS-Altera DE1 – B môn i n T - HBK Tp HCM CÁC BƯ C THÍ NGHI M K THU T S TRÊN KIT ALTERA DE1 Nh p file thi t k dùng mã Verilog Biên d ch Mô ph ng ch c năng No Thi t k úng? Yes Gán chân Phân tích và mô ph ng th i gian No t yêu c u th i gian? Yes N p kit và th m ch Hình 1: Các bư c th c hi n

- 3. Trang 3 TN KTS-Altera DE2 – B môn i n T - HBK Tp HCM Bư c 1. Ch y chương trình Quartus II: Hình 2: Màn hình chính Quartus® II.

- 4. Trang 4 TN KTS-Altera DE1 – B môn i n T - HBK Tp HCM Bư c 2. T o project m i: 1. Ch n File > New Project Wizard: Hình 3: File menu. 2. Ch n thư m c làm vi c, t tên cho project r i nh n Next: Hình 4: T o 1 project m i.

- 5. Trang 5 TN KTS-Altera DE1 – B môn i n T - HBK Tp HCM • Nh n Yes. Hình 5: Quartus® II t o thư m c m i cho project. 3. Không c n ph i ch n thêm file nào, nh n NEXT: Hình 6: Thêm file thi t k ã có s n. 4. Ch n chip Cyclone II EP2C20F484C7N, nh n NEXT. Hình 7: Ch n chip FPGA.

- 6. Trang 6 TN KTS-Altera DE1 – B môn i n T - HBK Tp HCM 5. Không c n ch n EDA TOOL nào, nh n Next: Hình 8: Ch n EDA tools. 6. B ng tóm t t các thông s cài t cho project như hình 9. Nh n Finish Hình 9: Tóm t t các thông s cài t cho project.

- 7. Trang 7 TN KTS-Altera DE1 – B môn i n T - HBK Tp HCM Chương trình s quay tr v màn hình chính: Hình 10: Màn hình Quartus® II cho project m i ư c t o.

- 8. Trang 8 TN KTS-Altera DE2 – B môn i n T - HBK Tp HCM Bư c 3. Nh p file thi t k dùng mã Verilog: 3.1. Ch n File > New, ch n Verilog HDL File, r i nh n OK. Hình 13: Ch n Verilog HDL file.

- 9. Trang 9 TN KTS-Altera DE2 – B môn i n T - HBK Tp HCM 3.2. T o file thi t k m i: ch n File > Save As, ch n Save as type = Verilog HDL File. t tên cho file. Ch n Add file to current project. Nh n Save Hình 14: t tên file. 3.3 Nh p chương trình dùng mã Verilog vào khung Text Editor. Lưu file: File > Save, ho c nh n Ctrl-S. Hình 15: Màn hình Quartus® II sau khi t o file.

- 10. Trang 10 TN KTS-Altera DE1 – B môn i n T - HBK Tp HCM Có th tùy ch n các tính năng c a Text Editor b ng cách ch n: Tools > Options > Text Editor. Hình 16: Cáctùych nchoTextEditor. • Có th dùng template nh p chương trình: Edit > Insert Template > Verilog HDL 3.4. ưa file thi t k vào project: ch n Assignments > Settings, ch n Files ho c ch n Project > Add/Remove Files in Project • N u ã dùng Quartus® II Text Editor và ã ch n Add file to current project như trong ph n 3.2 thì file thi t k s ư c n p th ng vào project. Hình 17: Tùy ch n các thông s cho project.

- 11. Trang 11 TN KTS-Altera DE1 – B môn i n T - HBK Tp HCM • N u chưa có thì ph i n p như sau: 1. Copy file thi t k vào thư m c làm vi c. 2. Nh n nút ... ch n file Hình 18: Ch n file 3. Ch n file c n thi t r i nh n Open. Sau ó nh n Add, OK. Bư c 4. Biên d ch chương trình thi t k : 4.1 Ch n Processing > Start Compilation, ho c nh n nút . Ch biên d ch chương trình cho n khi báo Successful (ho c unsuccessful) r i nh n OK Hình 19: Màn hình sau khi biên d ch thành công.

- 12. Trang 12 TN KTS-Altera DE1 – B môn i n T - HBK Tp HCM 4.2 Khi biên d ch xong chương trình s t ng hi n th Compilation Report. Report này cũng có th ư c m b ng cách ch n Processing > Compilation Report ho c nh n nút . Hình 20: K t qu biên d ch. • Thông báo l i: Hình 25: Thông báo biên d ch có l i. Hình 26: N i dung l i. Hình 27: Xác nh v trí l i

- 13. TN KTS-Altera DE1 – B môn i n T - HBK Tp HCM 13 Bư c 5. Gán chân c a project cho kit Altera DE 1: 5.1 Ch n Assignments > Import Assignments. Ch n file “DE1_pin_assignments.csv” – Nh n OK. Hình 24. Màn hình Import Assignments 5.2 Ch n Assignments > Assignment Editor. Ch n Category = Pin. • Double-click vào v t sáng highlight màu xanh dương c t “To”. R i gán các chân vào, ra tương ng. Hình 25. Drop-down menu hi n th tên các ngõ vào, ra. • Lưu file thi t k . Hình 27. Hoàn t t vi c gán chân Bư c 6. Mô ph ng m ch thi t k : 1. Ch n File > New - Ch n Vector Waveform File - Nh n OK. 2. Màn hình Waveform Editor như Hình 32. • Lưu vector waveform file (.vwf) • Ch n th i gian th c hi n mô ph ng t 0 n 200 ns b ng cách ch n Edit > End Time r i nh p 200 ns. • Ch n View > Fit in Window

- 14. TN KTS-Altera DE1 – B môn i n T - HBK Tp HCM 14 Hình 33. Màn hình Waveform Editor 3. Ch n Edit > Insert Node or Bus. Hình 34. H p tho i Insert Node or Bus. • Nh n nút Node Finder. Hình 35. Ch n nodes ưa vào Waveform Editor. • Ch n Filter = Pins: all r i nh n nút List. • Ch n nút >> r i nh n OK. • Nh n OK trong c a s hình 34. 4. Ch n các giá tr logic c a các ngõ vào th . Lưu vector waveform file.

- 15. TN KTS-Altera DE1 – B môn i n T - HBK Tp HCM 15 Hình 37. Ch n các giá tr logic c a các ngõ vào th 6.1 Th c hi n mô ph ng: (Functional Simulation) • Ch n Assignments > Settings – ch n Simulation mode = Functional r i nh n OK. Hình 38. Ch n Simulation mode = Functional. • Ch n Processing > Generate Functional Simulation Netlist. • B t u th c hi n mô ph ng b ng cách ch n Processing > Start Simulation, ho c nh n nút . Hình 39. K t qu mô ph ng.

- 16. TN KTS-Altera DE1 – B môn i n T - HBK Tp HCM 16 Bư c 7. L p trình cho FPGA trên kit Altera DE1: • Trên kit DE2 t SW19 = RUN (JTAG mode) • K t n i USB cáp t máy tính v i USB-Blaster trên kit DE1. • C p ngu n cho kit. • Ch n Tools > Programmer. Ch n Mode = JTAG. Ch n Hardware = USB-Blaster theo như Hình 42. • Ch n Check box Program/Configure. Hình 41. Màn hình programing. Hình 42. Màn hình ch n hardware. • Nh n nút Start b t u n p project vào kit DE1. Bư c 8. Th project v a thi t k : Ti n hành th project v a ư c n p trên kit DE1. N u mu n thay i thi t k trư c h t ph i t t màn hình Programmer r i th c hi n project m i t bư c 2.

- 17. TN KTS-Altera DE1 – B môn i n T - HBK Tp HCM 17 Bài thí nghi m 1 Switches, Lights, Multiplexers 1. Thí nghi m 1.1: Th c hi n m ch thí nghi m có ngõ vào là 10 công t c SW9−0, và ngõ ra là 10 èn LED màu LEDR9−0 dùng c tr ng thái c a các ngõ vào. // Chuơng trình Verilog ơn gi n cho bài TN 1.1: module tn1_1 (SW, LEDR); input [9:0] SW; // toggle switches output [9:0] LEDR; // red LEDs assign LEDR = SW; endmodule Các bư c c n th c hi n: 1. T o project m i. 2. Vi t chương trình Verilog cho bài TN 3. Gán chân & biên d ch project. 4. N p project vào kit TN. Th m ch. 2. Thí nghi m 1.2: • Cho m ch multiplexer 2 sang 1 như hình 2 v i ngõ vào ch n kênh s. N u s = 0 ngõ ra m s b ng ngõ vào x, và n u s = 1 thì ngõ ra m = y. x m s y a) Sơ m ch s s m 0 x x 0 m 1 y y 1 b) B ng s th t c) Ký hi u Hình 2. M ch multiplexer 2 sang 1. M ch có th mô t dùng mãVerilog như sau: assign m = ( s & x) ¡ (s & y); • Dùng 4 b multiplexer 2 sang 1 như hình 2 th c hi n m ch multiplexer 2 sang 1 - 4 bit như hình 3a. M ch có 2 ngõ vào nh phân 4 bit X và Y, và ngõ ra 4 bit M. N u s = 0 thì M = X, còn s = 1 thì M = Y.

- 18. TN KTS-Altera DE1 – B môn i n T - HBK Tp HCM 18 s x3 0 m3 y3 1 X3 0 m2 s Y3 1 4 X 0 4 M Y 1 4 x0 0 m0 y0 1 a) sơ m ch b) ký hi u Hình 3. M ch multiplexer 2 sang 1, 4 bit. Các bư c c n th c hi n: 1. T o project m i. 2. Vi t chương trình Verilog v i: s = SW9 và n i v i LEDR9 X = SW3-0 và n i v i LEDR3-0 Y = SW7-4 và n i v i LEDR7-4 M = LEDG3-0 3. Gán chân 4. Biên d ch project. 5. N p project vào kit TN. 6. Th m ch b ng cách thay i các công t c SW r i theo dõi các èn LED xanh, . 3. Thí nghi m 1.3: • Dùng 3 b multiplexer 2 sang 1 như hình 2 th c hi n m ch multiplexer 4 sang 1 như hình 4a. M ch có 4 ngõ vào u, v, w và x; 1 ngõ ra m; 2 ngõ vào ch n kênh s1 s0 s1 s0 u 0 0 v 1 1 m w 0 x 1 a) sơ m ch

- 19. TN KTS-Altera DE1 – B môn i n T - HBK Tp HCM 19 0 0 u 0 1 v 1 0 w 1 1 x s x s1 s0 m 1 s0 u v 00 01 w 10 m 11 x b) b ng s th t c) ký hi u Hình 4. M ch multiplexer 4 sang 1 • Tương t dùng 2 m ch multiplexer4→1như hình 4a th c hi n m ch multiplexer4→1-2bitnhư hình5 s1 s0 U 2 2 V 00 2 01 2 W 10 M 2 11 X Hình 5. M ch multiplexer 4 sang 1 - 2 bit Các bư c c n th c hi n: 1. T o project m i. 2. Vi t chương trình Verilog v i: s1 s0 = SW9-8 và n i v i LEDR9-8 U-X = SW7-0 và n i v i LEDR7-0 M = LEDG1-0 3. Gán chân 4. Biên d ch project. 5. N p project vào kit TN. 6. Th m ch b ng cách thay i các công t c SW r i theo dõi các èn LED xanh, .

- 20. TN KTS-Altera DE1 – B môn i n T - HBK Tp HCM 20 4. Thí nghi m 1.4: Th c hi n b gi i mã có 2 ngõ vào c1c0 và 7 ngõ ra t 0 n 6 dùng hi n th các ký t trên b hi n th 7 o n như hình 6. B ng 1 li t kê các ký t c n hi n th (g m H,E,L và ký t O) tương ng v i các ngõ vào c1c0. Các ngõ ra tích c c m c logic 0. c1 7-segment decoder c0 0 5 6 1 4 2 3 Hình 6. B gi i mã 7 o n c1 c0 Ký t 0 0 H 0 1 E 1 0 L 1 1 O B ng1. B ng mã ch Các bư c c n th c hi n: 1. T o project m i. 2. Vi t chương trình Verilog v i: o Các ngõ vào c1c0 n i v i các công t c SW1-0 o Các ngõ ra 0 – 6 n i v i HEX00, HEX01…..HEX06 3. Gán chân 4. Biên d ch project. 5. N p project vào kit TN. 6. Th m ch b ng cách thay i các công t c SW1−0 r i quan sát b hi n th 7 o n.

- 21. TN KTS-Altera DE1 – B môn i n T - HBK Tp HCM 21 2 2 2 5. Thí nghi m 1.5: Th c hi n m ch i n hi n th “ch xoay” như hình 7 ho t ng theo b ng 2. Các công t c SW7−0 dùng t o ký t và SW9−8 dùng ch n ký t hi n th . SW9 SW8 SW7 – 6 2 SW5 – 4 SW3 – 2 SW1 – 0 0 0 0 1 1 0 1 1 2 7-segment decoder 0 7 5 6 1 4 2 3 Hình 7. M ch có th ch n & hi n th 1 trong 4 ký t . B ng 2. Hi n th ch xoay HELLO. module part5 (SW, HEX0); input [9:0] SW; // toggle switches output [0:6] HEX0; // 7-seg displays wire [1:0] M; mux 2bit 4to1 M0 (SW[9:8], SW[7:6], SW[5:4], SW[3:2], SW[1:0], M); char 7seg H0 (M, HEX0); endmodule // implements a 2-bit wide 4-to-1 multiplexer module mux 2bit 4to1 (S, U, V, W, X, M); input [1:0] S, U, V, W, X; output [1:0] M; . . . code not shown endmodule // implements a 7-segment decoder for H, E, L and O module char 7seg (C, Display); input [1:0] C; // input code output [0:6] Display; // output 7-seg code . . . code not shown endmodule Hình 8. Chương trình g i ý cho m ch i n hình 7. SW9 SW8 Hi n th 0 0 H 0 1 E 1 0 L 1 1 O

- 22. TN KTS-Altera DE1 – B môn i n T - HBK Tp HCM 22 Binary value 0000 Decimal 0 digits 0 0001 0 1 0010 0 2 . . . . . . . . . 1001 0 9 1010 1 0 1011 1 1 1100 1 2 1101 1 3 1110 1 4 1111 1 5 Bài thí nghi m 2 Numbers & Displays ây là bài thí nghi m thi t k m ch t h p th c hi n b bi n i s nh phân sang s th p phân và m ch c ng hai s BCD. 1. Thí nghi m 2.1: Dùng các èn 7 o n HEX1 và HEX0 hi n th các s th p phân t 0 n 9. Giá tr hi n th thay i ư c b ng các công t c SW7−4 và SW3−0 tương ng. • Các bư c c n th c hi n: 1. T o project m i. 2. Vi t chương trình Verilog cho bài TN 3. Gán chân & biên d ch project. 4. N p project vào kit TN. Th m ch b ng cách thay i các công t c và quan sát các èn hi n th . 2. Thí nghi m 2.2: Th c hi n 1 ph n c a m ch chuy n i s nh phân 4 bit V = v 3v2 v1 v0 thành s th p phân D = d1 d0 như hình 1, b ng 1. M ch bao g m m ch so sánh ( ki m tra V > 9), m ch multiplexer và m ch A (chưa c n th c hi n m ch B và b gi i mã 7 o n). M ch s có ngõ vào V 4 bit, ngõ ra M 4 bit và ngõ ra z. B ng1. B ng giá tr chuy n i nh phân th p phân. • Các bư c c n th c hi n: 1. T o project m i. Vi t chương trình 2. Biên d ch project và th c hi n mô ph ng 3. Vi t thêm o n chương trình cho m ch B và m ch gi i mã 7 o n. Dùng các công t c SW3−0 nh p s nh phân V và các èn 7 o n HEX1, HEX0 hi n th s th p phân d1 d0 4. Biên d ch l i r i n p project vào kit TN. 5. Th m ch: thay i giá tr V và quan sát các èn hi n th .

- 23. TN KTS-Altera DE1 – B môn i n T - HBK Tp HCM 23 z Comparator v3 0 m3 0 1 Circuit B d1 0 7 5 6 1 4 2 3 v2 0 m2 1 v1 0 1 m1 v0 0 m0 1 7-segment 7 decoder d0 0 5 6 1 4 2 3 Circuit A Hình 1. M ch chuy n i nh phân-th p phân. 3. Thí nghi m 2.3: Cho m ch c ng toàn ph n (FA) như hình 2a v i các ngõ vào a, b, and ci, các ngõ ra s và co. cos = a + b + ci. Dùng 4 m ch c ng FA như trên th c hi n m ch c ng 4 bit như hình 2d.

- 24. TN KTS-Altera DE1 – B môn i n T - HBK Tp HCM 24 0 0 0 0 0 0 0 1 0 1 0 1 0 0 1 0 1 1 1 0 1 0 0 0 1 1 0 1 1 0 1 1 0 1 0 1 1 1 1 1 oc s ci a s ci a FA b 0 b co 1 a) M ch c ng FA b) Ký hi u b a ci co s b3 a3 c3 b2 a2 c2 b1 a1 c1 b0 a0 cin FA FA FA FA cout s3 s2 s1 s0 c) B ng s th t d) M ch c ng 4 bit Hình 2. M ch c ng. • Các bư c c n th c hi n: 1. T o project m i và vi t chương trình Verilog cho m ch c ng: • N i các ngõ vào A, B và cin v i các công t c tương ng SW7−4 , SW3−0 và SW8 và v i các èn LED màu LEDR • N i các ngõ ra cout và S v i các èn LED màu xanh LEDG 2. Gán chân, biên d ch và n p project vào kit TN 3. Th m ch b ng cách thay i các giá tr khác nhau c a A, B và c in, quan sát các èn hi n th . 4. Thí nghi m 2.4: Th c hi n m ch c ng 2 s BCD. Ngõ vào c a m ch là 2 s A, B và ngõ vào cho s nh cin. Ngõ ra là s BCD t ng S1S0 và s nh cout. • Các bư c c n th c hi n: 1. T o project m i cho m ch c ng s BCD. Ph i th c hi n m ch c ng 2 s 4 bit A, B (thí nghi m 2.3) và 1 m ch chuy n i 5 bit t ng s3s2s1s0co thành 2 s BCD S1S0 (thí nghi m 2.2) 2. Vi t chương trình Verilog: • N i các ngõ vào A, B và cin v i các công t c tương ng SW7−4 , SW3−0 và SW8 và v i các èn LED màu LEDR7−0 • N i các ngõ ra cout và S v i các èn LED màu xanh LEDG4−0 • Dùng các èn 7 o n HEX3, HEX2 hi n th giá tr c a 2 s A và B và HEX1, HEX0 hi n th k t qu S1S0 . 3. Gán chân, biên d ch và n p project vào kit TN 4. Th m ch b ng cách thay i các giá tr khác nhau c a A, B và c in, quan sát các èn hi n th . 5. Thí nghi m 2.5: Thi t k m ch t h p chuy n i 1 s nh phân 6 bit thành s th p phân dư i d ng 2 s BCD. Dùng các công t c SW5−0 nh p s nh phân và các èn 7 o n HEX1 và HEX0 hi n th s th p phân.

- 25. TN KTS-Altera DE1 – B môn i n T - HBK Tp HCM 25 Bài thí nghi m 3 Latches, Flip-flops, Registers 1. Thí nghi m 3.1: Hình 1 mô t m ch RS latch dùng c ng logic. Có 2 cách dùng Verilog mô t m ch này: dùng c ng logic (hình 2a) và dùng công th c logic (hình 2b). R R_g Qa (Q) Clk Qb S S_g Hình 1. M ch RS latch dùng c ng logic. // A gated RS latch module part1 (Clk, R, S, Q); input Clk, R, S; output Q; wire R_g, S_g, Qa, Qb /* synthesis keep */ ; and (R_g, R, Clk); and (S_g, S, Clk); nor (Qa, R_g, Qb); nor (Qb, S_g, Qa); assign Q = Qa; endmodule Hình 2a. Dùng c ng logic mô t m ch RS latch. // A gated RS latch module part1 (Clk, R, S, Q); input Clk, R, S; output Q; wire R_g, S_g, Qa, Qb /* synthesis keep */ ; assign R_g = R & Clk; assign S_g = S & Clk; assign Qa = (R_g ¡ Qb); assign Qb = (S_g ¡ Qa); assign Q = Qa; endmodule Hình 2b. Dùng công th c logic mô t m ch RS latch.

- 26. TN KTS-Altera DE1 – B môn i n T - HBK Tp HCM 26 Có 2 cách th c hì n: dùng 1 LUT 4 ngõ vào (hình 3a) và dùng 4 LUT 2 ngõ vào (hình 3b). R Clk S 4-LUT Qa (Q) (a) RS latch ch dùng 1 b ng tham chi u 4 ngõ vào. R 4-LUT R_g 4-LUT Qa (Q) Clk 4-LUT S S_g 4-LUT Qb (b) RS latch dùng 4 b ng tham chi u 2 ngõ vào. Hình 3. Các cách th c hi n m ch RS latch • Các bư c c n th c hi n: 1. T o project RS latch 2. Vi t chương trình Verilog theo hai cách 2a và 2b. 3. Biên d ch. Dùng ti n ích RTL Viewer so sánh v i sơ m ch hình 1. Dùng ti n ích Technology Viewer so sánh v i sơ m ch hình 3b. 4. T o Vector Waveform File (.vwf) cho các ngõ vào/ra. T o d ng sóng cho các ngõ vào R và S r i dùng ti n ích Quartus II Simulator quan sát các d ng sóng R_g, S_g, Qa và Qb

- 27. TN KTS-Altera DE1 – B môn i n T - HBK Tp HCM 27 2. Thí nghi m 3.2: Cho m ch D latch dùng c ng như hình 4. D S S_g Qa (Q) Clk Qb R R_g Hình 4. M ch D latch dùng c ng logic. • Các bư c c n th c hi n: 1. T o project m i v i chương trình Verilog d ng 2b cho m ch D latch. 2. Biên d ch chương trình. Dùng ti n ích Technology Viewer kh o sát m ch. 3. Mô ph ng ki m tra ho t ng c a m ch. 4. Dùng công t c SW0 cho ngõ vào D, và SW1 cho ngõ vào Clk. N i ngõ ra Q n LEDR0. 5. Biên d ch chương trình l i và n p project vào kit TN. 6. Th m ch b ng cách thay i các ngõ vào D, Clk và quan sát ngõ ra Q.

- 28. TN KTS-Altera DE1 – B môn i n T - HBK Tp HCM 28 3. Thí nghi m 3.3: Cho m ch master-slave D flip-flop hình 5. Master Slave Qm Qs D D Q D Q Q Clock Clk Q Clk Q Q Hình 5. M ch master-slave D flip-flop. • Các bư c c n th c hi n: 1. T o project m i dùng 2 D flip-flop c a thí nghi m 3.2. 2. Dùng công t c SW 0 cho ngõ vào D, và SW1 cho ngõ vào Clk. N i ngõ ra Q n LEDR0. 3. Biên d ch chương trình. 4. Dùng ti n ích Technology Viewer kh o sát m ch. Mô ph ng ki m tra ho t ng c a m ch. 5. Th m ch b ng cách thay i các ngõ vào D, Clk và quan sát ngõ ra Q. 4. Thí nghi m 3.4: Cho m ch i n hình 6 v i D latch, D flip- flop kíck c nh lên và D flip- flop kíck c nh xu ng.

- 29. TN KTS-Altera DE1 – B môn i n T - HBK Tp HCM 29 D D Q Qa Clock Clk Q Qa D Q Qb Q Qb D Q Qc Q Qc (a) Sơ m ch Clock D Qa Qb Qc (b) Gi n d th i gian Hình 6. Sơ m ch và d ng sóng c a thí nghi m 3.4. • Các bư c c n th c hi n: 1. T o project m i. 2. Vi t chương trình d a trên o n chương trình g i ý như hình 7. 3. Biên d ch chương trình. 4. Dùng ti n ích Technology Viewer kh o sát m ch. 5. Mô ph ng ki m tra ho t ng c a m ch. So sánh ho t ng c a các ph n t trong m ch. module D_latch (D, Clk, Q); input D, Clk; output reg Q; always @ (D, Clk) if (Clk) Q = D; endmodule Hình 7. Chương trình g i ý cho D latch.

- 30. TN KTS-Altera DE1 – B môn i n T - HBK Tp HCM 30 Bài thí nghi m 4 Counters 1. Thí nghi m 4.1: Cho m ch m ng b 4 bit dùng 4 T flip-flops như hình 1. Enable T Q Clock Q T Q T Q T Q Q Q Q Clear Hình 1. B m 4 bit. • Các bư c c n th c hi n: 1. T o project m i th c hi n b m 16 bit dùng 4 m ch m như hình 1. Biên d ch chương trình. Ghi nh n s ph n t logic (LEs) ã ư c dùng? T n s ho t ng t i a (Fmax) c a m ch m là bao nhiêu? 2. Mô ph ng ho t ng c a m ch. 3. Gán thêm nút nh n KEY0 làm ngõ vào Clock, các công t c SW1, SW0 làm ngõ vào Enable, Reset và các èn 7 o n HEX3-0 hi n th giá tr th p l c phân c a ngõ ra m ch m. 4. Biên d ch l i và n p project vào kit TN. 5. Th ho t ng c a m ch b ng cách thay i các công t c và quan sát các èn 7 o n. 6. Th c hi n m ch m 4 bit r i dùng ti n ích RTL Viewer quan sát m ch và so sánh v i m ch i n hình 1. 2. Thí nghi m 4.2: Th c hi n l i thí nghi m 4.1 dùng mã Verilog sau: Q <= Q + 1; Biên d ch chương trình. So sánh s ph n t logic (LEs) ã ư c dùng, t n s ho t ng t i a (Fmax) c a m ch m. Dùng RTL Viewer kh o sát và nh n xét nh ng khác bi t so v i thí nghi m 4.1.

- 31. TN KTS-Altera DE2 – B môn i n T - HBK Tp HCM 31 3. Thí nghi m 4.3: Dùng module có s n trong thư vi n LPM (Library of Parameterized Modules) th c hi n m ch m 16 bit. Thay i LPM cho phù h p, như Enable, Reset. 4. Thí nghi m 4.4: Th c hi n m ch ng h m giây t 0 n 9s hi n th trên èn 7 o n HEX 0. Ph i th c hi n 1 m ch m t o th i gian 1s t xung clock 50 MHz có s n trên kit TN. 5. Thí nghi m 4.5: Th c hi n m ch hi n th ch HELLO lên 4 èn 7 o n HEX 3 − 0, d ch t ph i sang trái v i th i kho ng 1s theo m u như b ng 1. Clock cycle Displayed pattern 0 H 1 H E 2 H E L 3 H E L L 4 E L L O 5 L L O 6 L O 7 O 8 H . . . and so on B ng1. èn ch ch y HELLO.