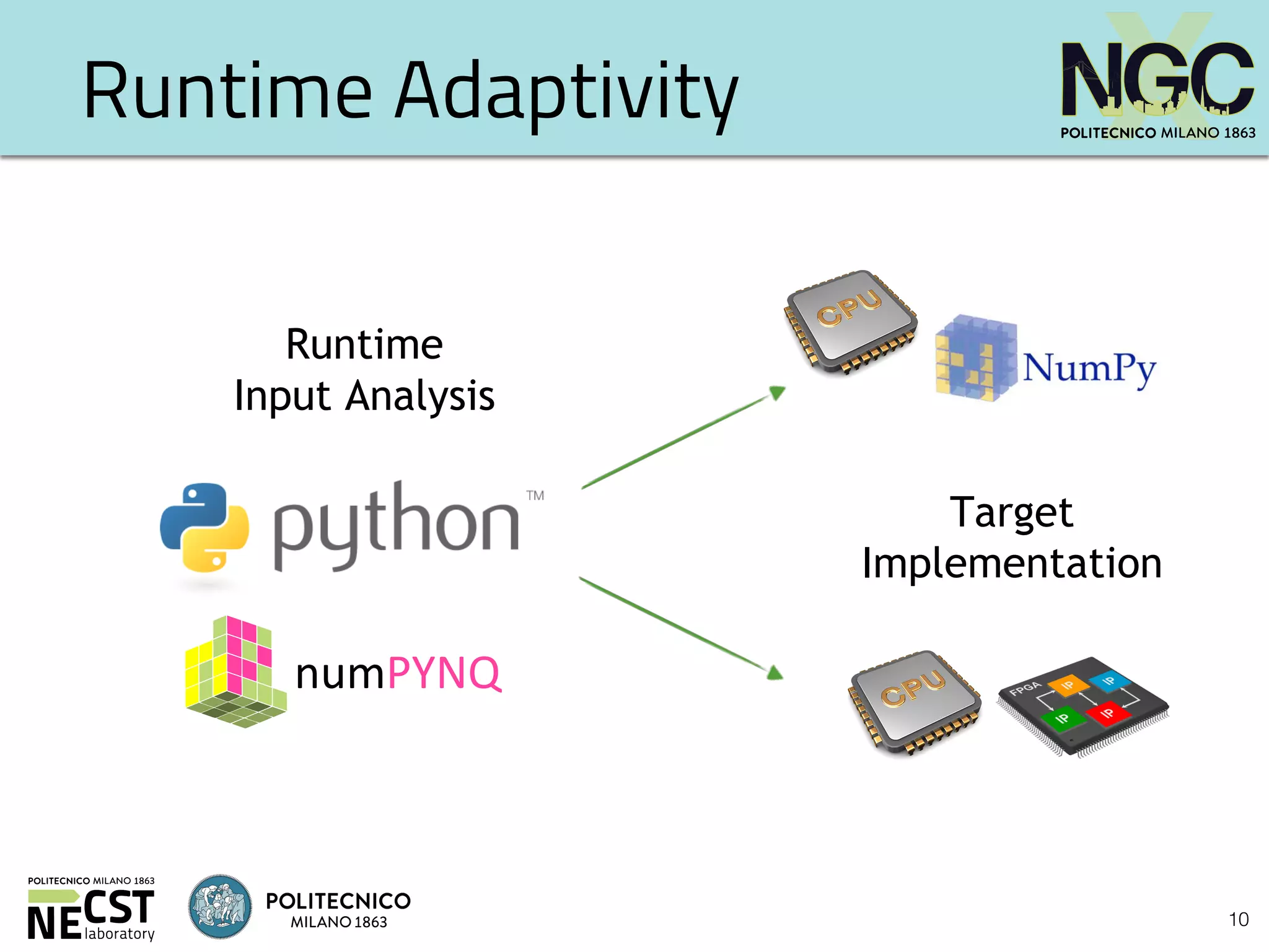

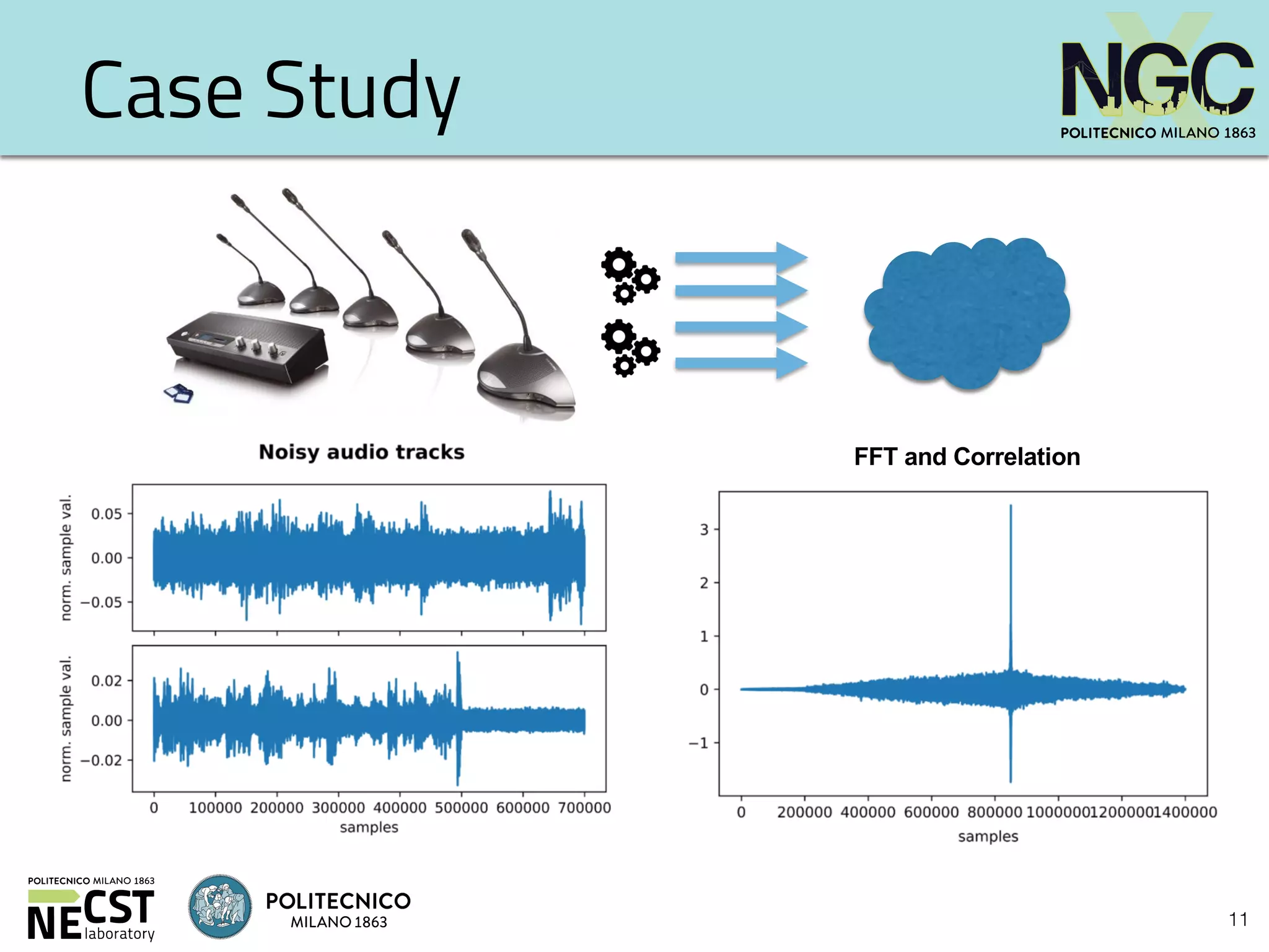

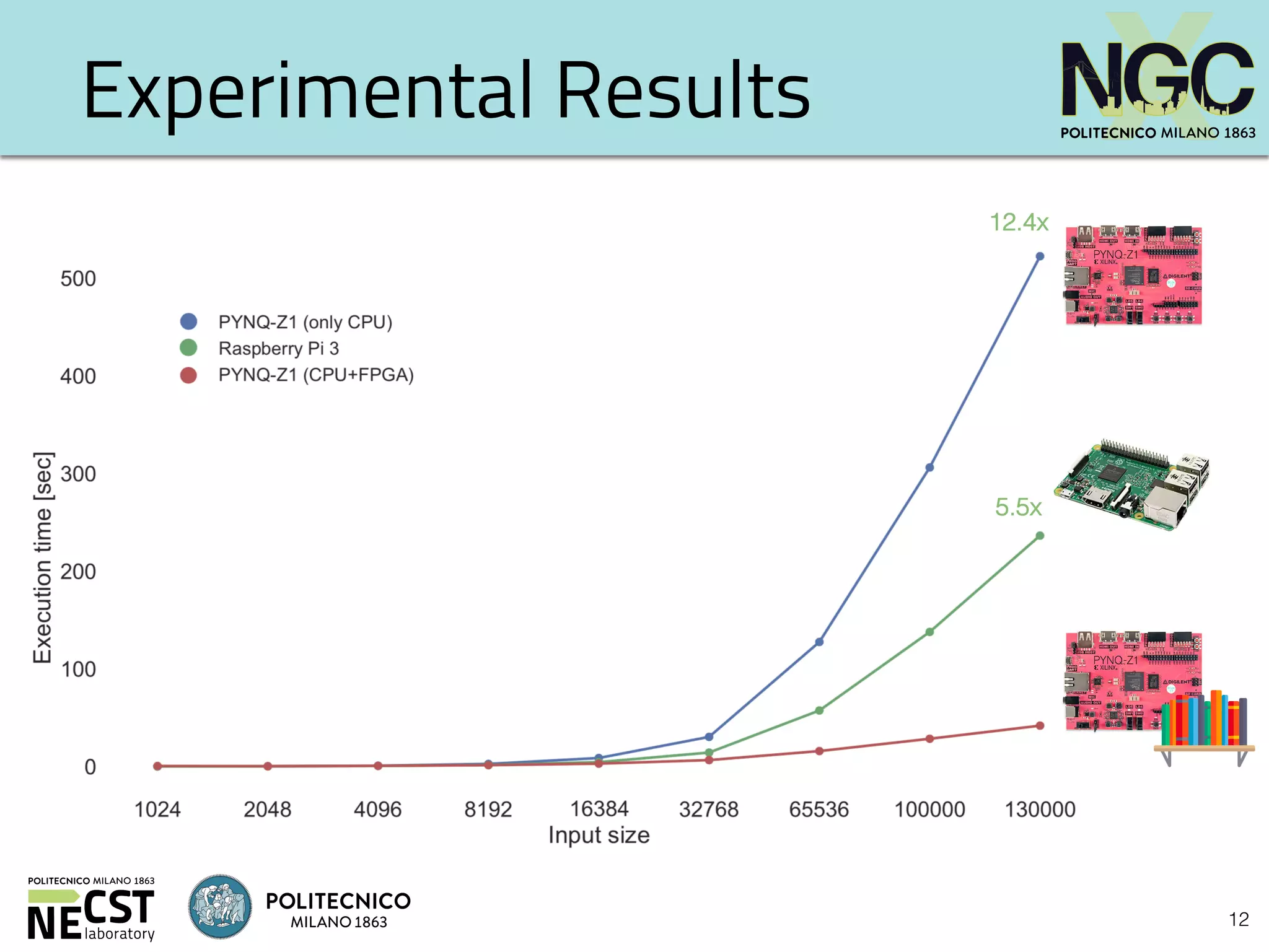

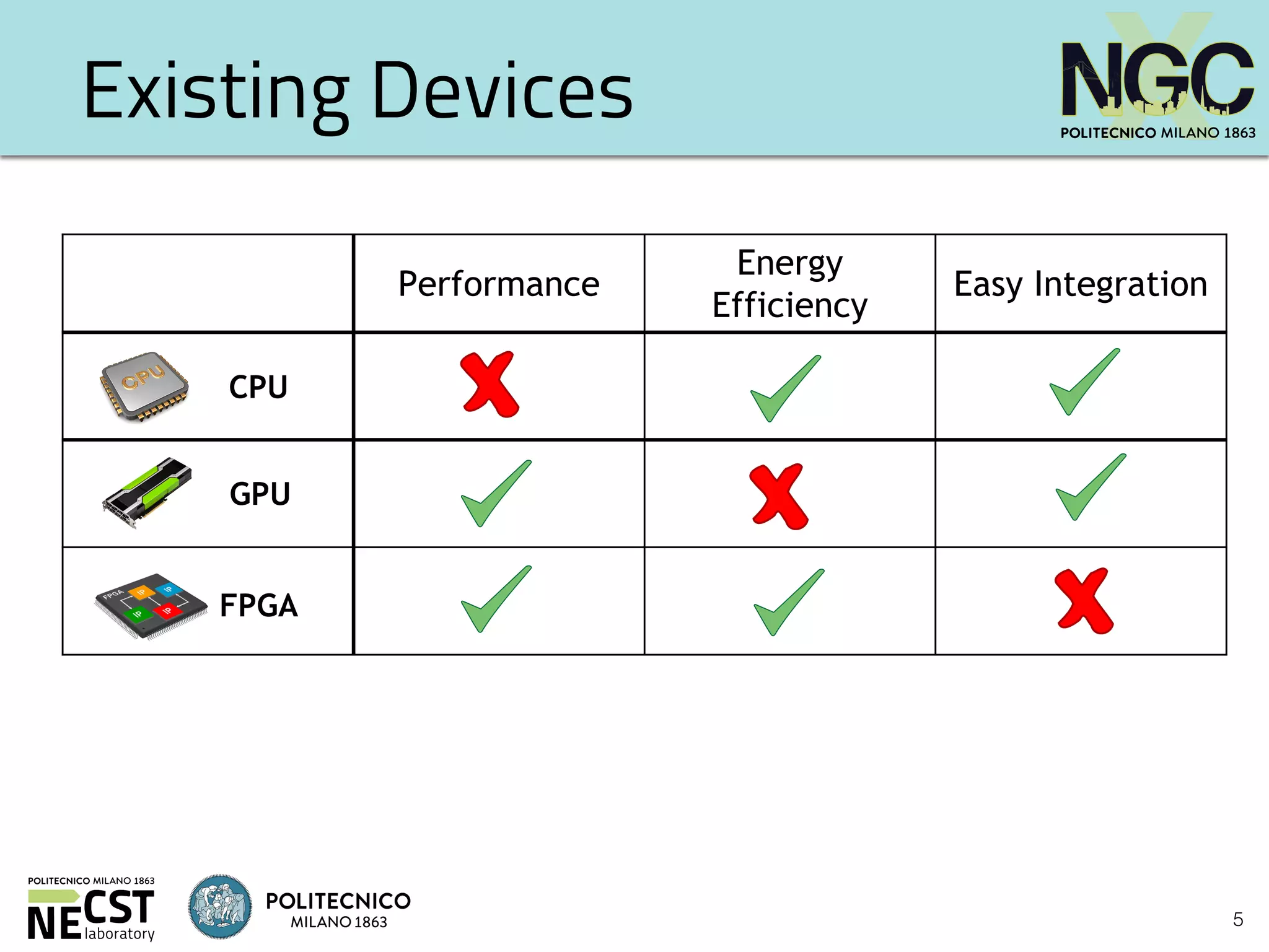

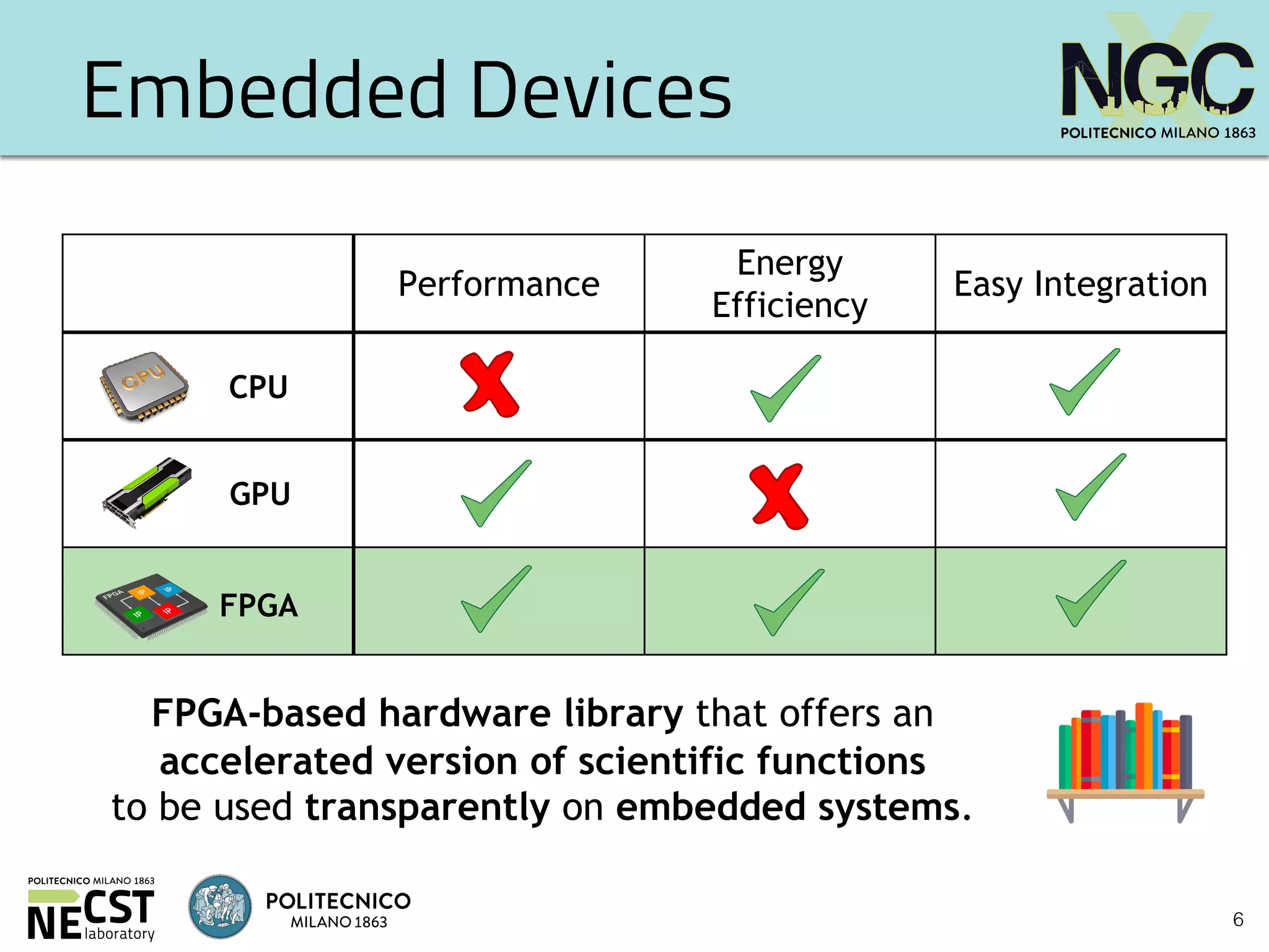

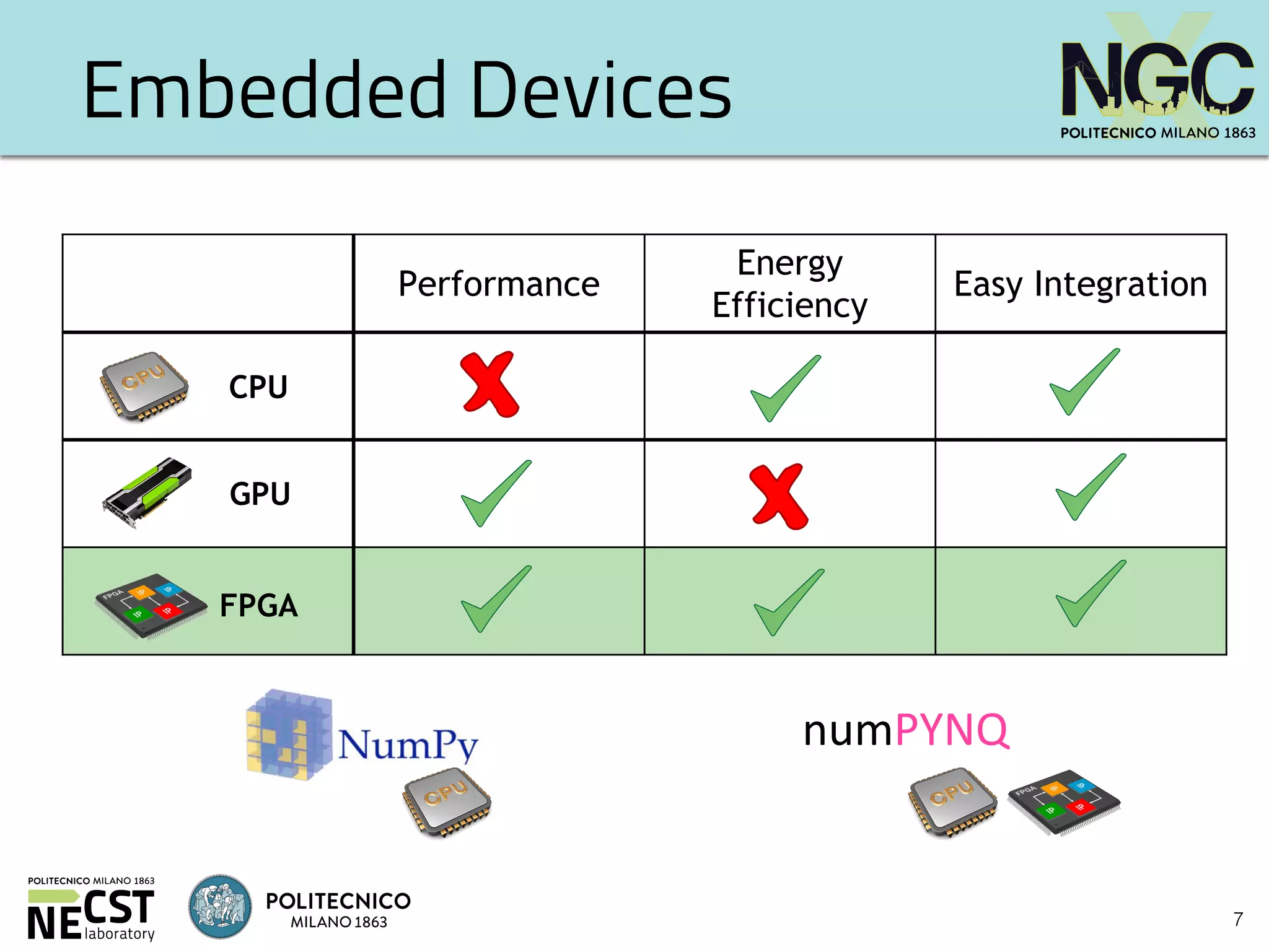

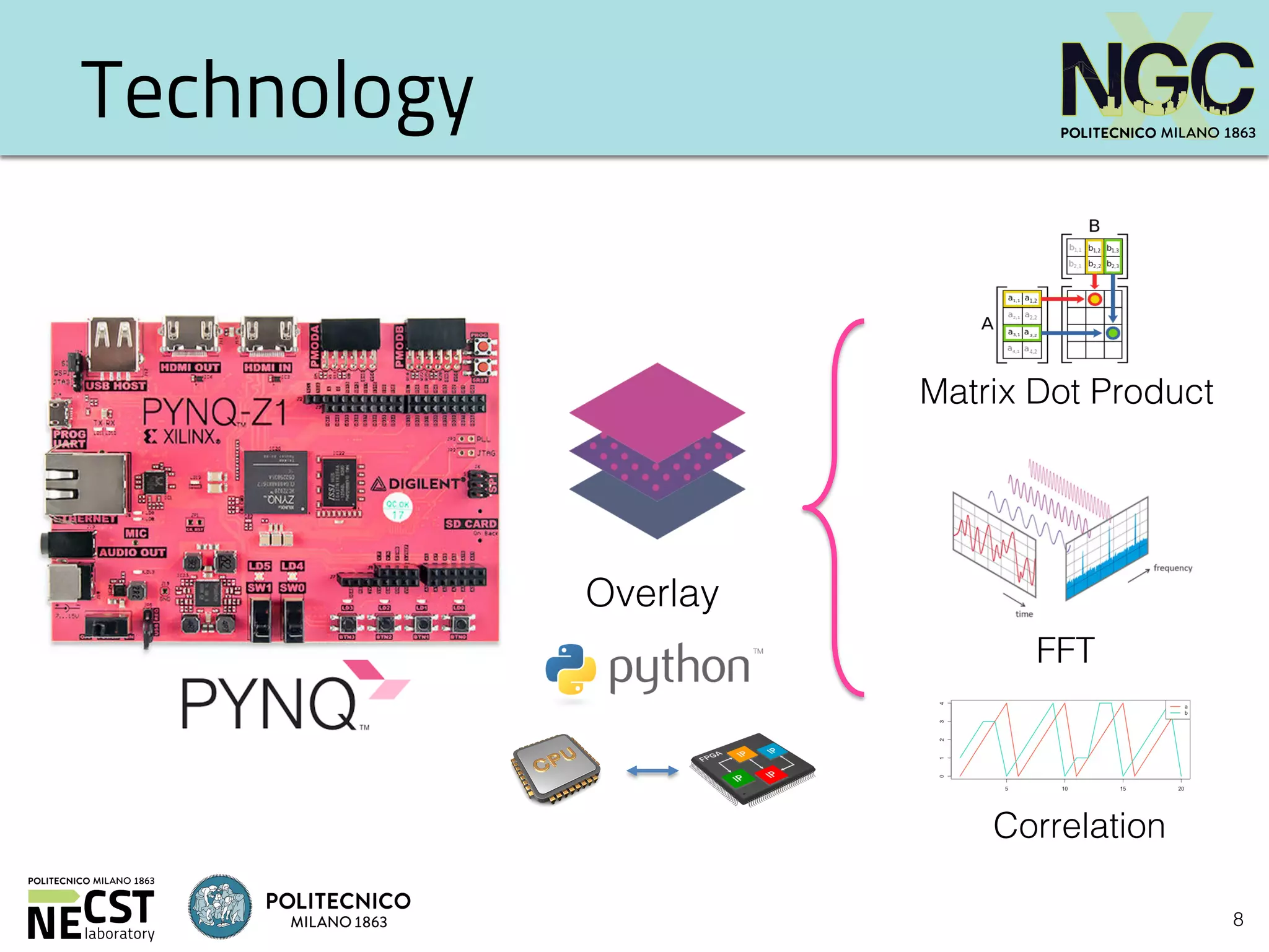

The document discusses enabling transparent hardware acceleration on Zynq SoC for Python data science applications, emphasizing the need for efficient processing of large datasets in real-time. It presents the NumpyQ framework, which utilizes FPGA-based libraries for accelerated scientific functions on embedded systems, achieving significant performance improvements. Experimental results highlight the advantages of using both CPU and FPGA, demonstrating enhanced execution times for various computational tasks.

![9

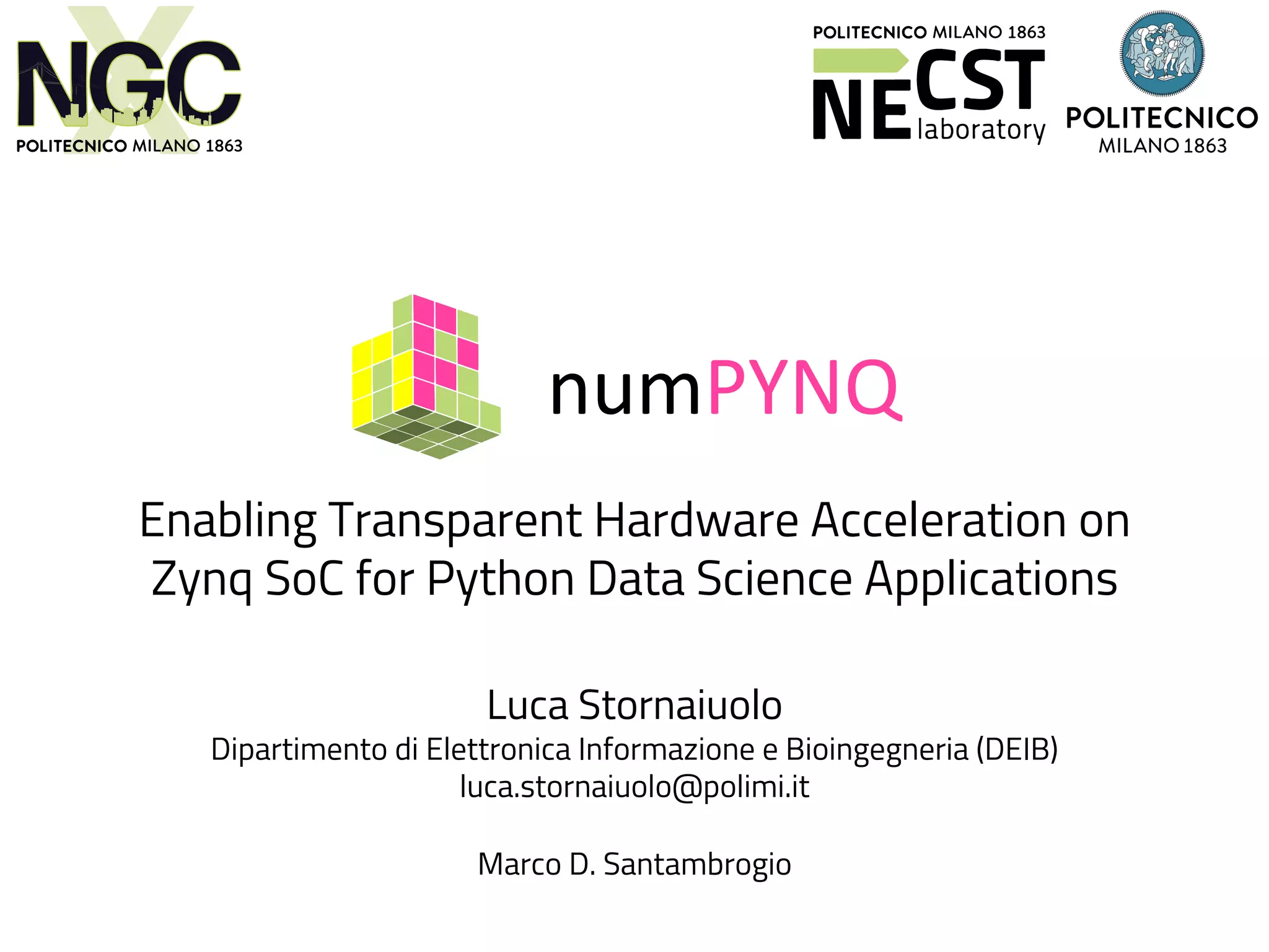

Matrix Dot Product

0

25

50

75

16

64

128

256

384

512

768

1024

Input size

Executiontime[sec]

PYNQ-Z1 (only CPU)

PYNQ-Z1 (CPU+FPGA)

0.00

0.01

0.02

0.03

0.04

16

32

64

100

125

150

Input sizeExecutiontime[sec]

PYNQ-Z1 (only CPU)

PYNQ-Z1 (CPU+FPGA)

Pipelined Dot Product

for Non-Fixed size Matrix

Parallel Dot Product

for Fixed size Matrix

3.5x

6.1x](https://image.slidesharecdn.com/numpynq-190519154058/75/numPYNQ-accelerating-NumPy-on-PYNQ-9-2048.jpg)