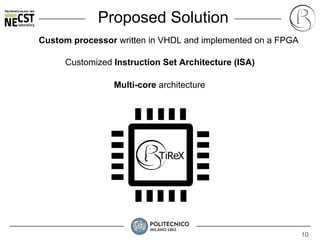

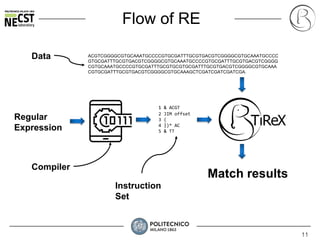

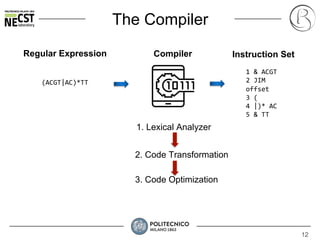

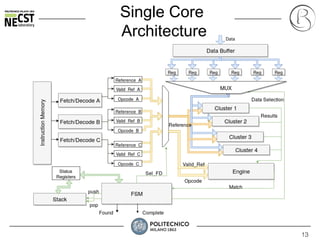

This document presents the architecture and implementation of a customized instruction set for tiled regular expressions matching, aimed at improving flexibility and performance. It discusses various components including a regular expression compiler, performance analysis on different architectures, and the proposed multi-core solution implemented on an FPGA. The results demonstrate significant speedups compared to traditional approaches, highlighting the advantages of the custom design.

![14

Board Test 1 Test 2 Test 3

Flex

Intel i7, 2.80 GHz

Exec. Time [µs] 271 121 263

Speedup 1X 1X 1X

Grep (Xeon)

Exec. Time [µs] 205 108.11 336.73

Speedup 1.32X 1.11X 0.78X

PYNQ-Z1

8-core, 70.5 MHz

Exec. Time [µs] 7.2 8.21 30.3

Speedup 37.63X 14.73X 8.67X

VC707

16-core, 130.1 MHz

Exec. Time [µs] 2.07 4.54 3.36

Speedup 130.9X 26.65X 78.27X

VU9P (AWS)

16-core, 202.7 MHz

Exec.Time [µs] 1.03 0.75 2.96

Speedup 263.11X 161.33X 88.85X

Performance Analysis

Latency Dataset

Baseline](https://image.slidesharecdn.com/tirexpitchvirtualngc-200731093615/85/TiReX-Tiled-Regular-eXpressionsmatching-architecture-14-320.jpg)