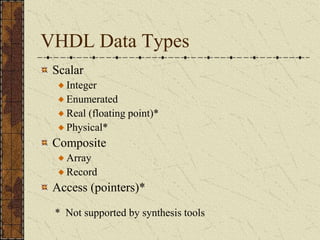

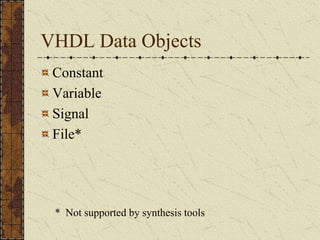

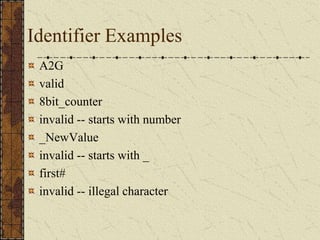

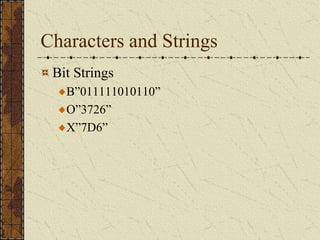

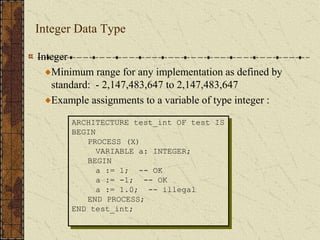

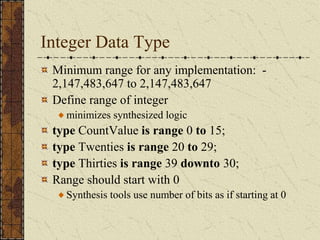

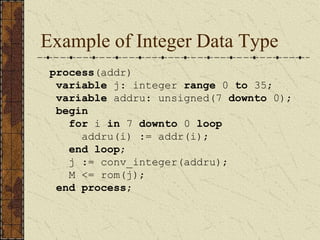

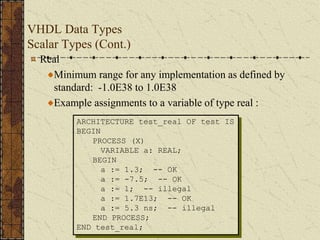

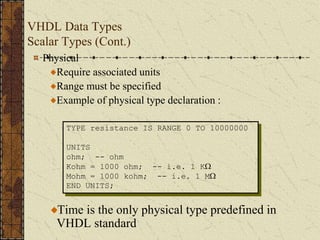

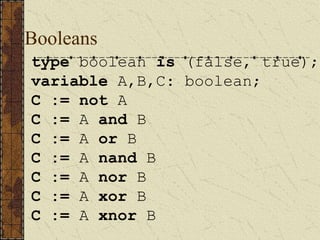

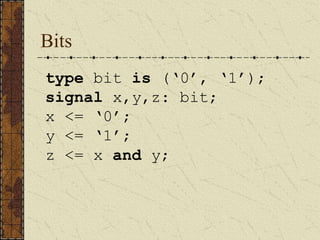

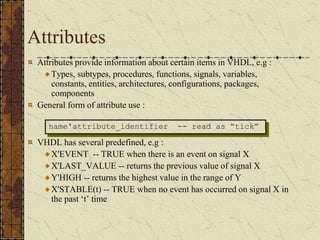

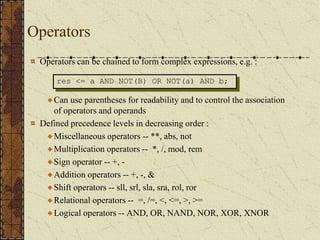

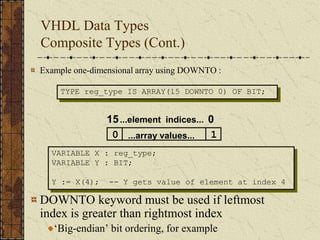

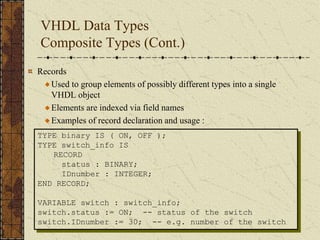

The document discusses VHDL data types, covering scalar types like integer, boolean, and real, along with composite types such as arrays and records. It includes guidelines for variable declarations, supported ranges, and examples, emphasizing the importance of constrained types for synthesis. Additionally, it provides information on character and string representation, operators, and attributes within VHDL.