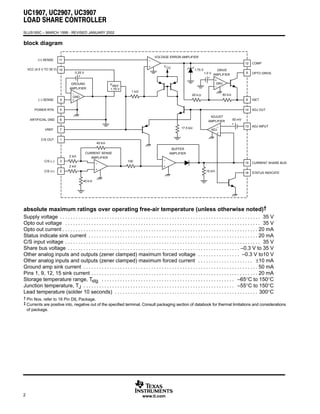

This document describes the UC1907, UC2907, and UC3907 load share controller ICs. These ICs allow multiple independent power modules to share load current proportionately by controlling each module's power stage based on a common current share bus voltage. Key features include accurate voltage and current sensing and amplification, adjustable current sharing through independent voltage feedback loops, and designation of a master module to ensure current matching within 2.5% across modules. The IC resides on each power module to provide closed-loop voltage control based on the current share bus signal.