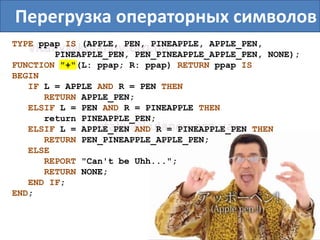

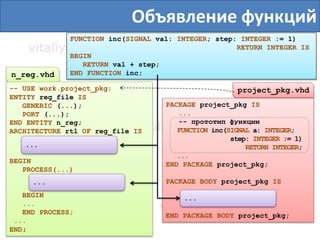

Документ описывает функции в языке VHDL, их структуры, декларации и использования. Уделяется внимание различиям между процедурами и функциями, а также правилам их вызова, передаче параметров и спецификациям возвратных значений. Также рассматривается создание функций с побочными эффектами и функции разрешения для управления множественными источниками данных.

![Куланов В.А.

[v.kulanov@csn.khai.edu]

Подпрограммы.

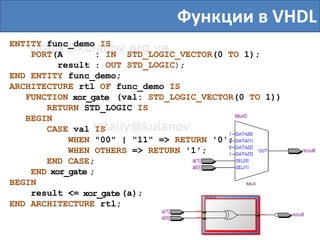

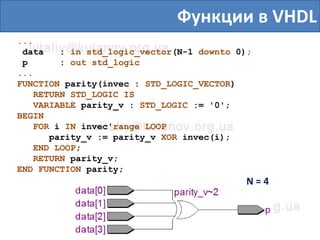

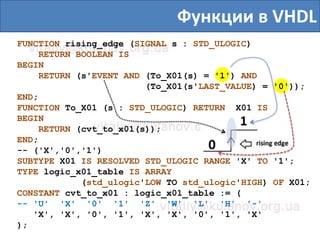

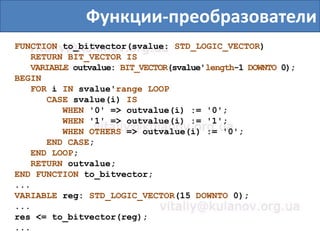

Функции в языке VHDL

«Технологии проектирования

компьютерных систем»](https://image.slidesharecdn.com/lecturevhdlfunctions-170514201021/85/Subprograms-in-VHDL-Functions-in-VHDL-1-320.jpg)

![Декларация функции в VHDL

[PURE|IMPURE]

FUNCTION name[(parameters_list)] RETURN type_mark IS

{subprogram_declarative_item}

BEGIN

{sequential_statement}

END [FUNCTION] [name];

SIGNAL, FILE, TYPE,

SUBTYPE, PROCEDURE,

FUNCTION, VARIABLE,

CONSTANT, ...-- последовательные операторы

a := 5

FOR … LOOP … END LOOP;

...

IF … THEN … ELSE … END IF;

Формальные

параметры

Можетлифункцияиметь

«побочныйэффект»?

(поумолчанию-PURE)

Тип возвращаемого

значения

Имя функции:

Идентификатор

Операторный символ («+», «*»)](https://image.slidesharecdn.com/lecturevhdlfunctions-170514201021/85/Subprograms-in-VHDL-Functions-in-VHDL-3-320.jpg)

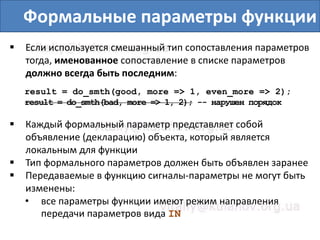

![Формальные параметры функции

...FUNCTION name[(parameter_list)] RETURN...IS

([CONSTANT|SIGNAL|FILE] identifier {,…}:

type_indication [:= expression] {;…})

Имя/Идентификатор

параметра

Класс параметра,

CONSTANT по умолчанию

(если класс явно не задан)

Тип параметра Значение по умолчанию

FUNCTION inc (a: BIT_VECTOR; step: INTEGER := 1) RETURN BIT_VECTOR;

FUNCTION "*" (a, b: fruits) RETURN fruits;

FUNCTION add_signals (SIGNAL in1, in2: REAL) RETURN REAL;

TYPE int_data IS FILE OF NATURAL;

FUNCTION end_of_file (FILE file_name: int_data) RETURN BOOLEAN;](https://image.slidesharecdn.com/lecturevhdlfunctions-170514201021/85/Subprograms-in-VHDL-Functions-in-VHDL-5-320.jpg)

![Вызов функции в VHDL

Вызов функции в исходном коде всегда является частью

выражения (операции присваивания, условные операторы и

т.д.): ... name[(parameter_list)] ...

Список фактических параметров

([parameter_name =>] expression|identifier|OPEN, {…})

Формальный параметр

Два типа сопоставления:

Именованное (=>)

Позиционное

Фактический параметр

выражение (константное значение)

имя/идентификатор сигнала, константы, файлового дескриптора

OPEN – параметр не используется или используется значение по

умолчанию](https://image.slidesharecdn.com/lecturevhdlfunctions-170514201021/85/Subprograms-in-VHDL-Functions-in-VHDL-6-320.jpg)

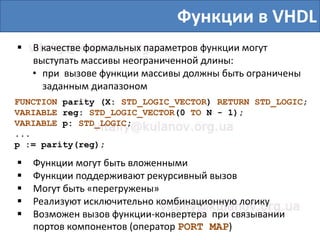

![Функции в VHDL

Тело функции должно содержать как минимум один оператор

RETURN:

[label:] RETURN expression;

Метка Возвращаемое значение

Тело функции НЕ должно содержать оператор присваивания

значения сигналу (<=) и оператор ожидания WAIT

В теле функции нельзя вызывать процедуру, в теле которой

находится оператор ожидания WAIT

В декларативной части функции могут быть объявлены

«локальные» переменные (VARIABLE), значение которых

инициализируется заново при каждом новом вызове

функции](https://image.slidesharecdn.com/lecturevhdlfunctions-170514201021/85/Subprograms-in-VHDL-Functions-in-VHDL-9-320.jpg)