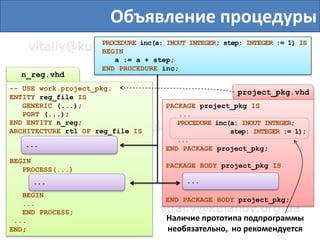

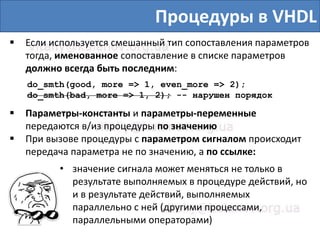

Документ рассматривает подпрограммы, в частности процедуры и функции в языке VHDL, акцентируя внимание на их структуре, синтаксисе и особенностях использования. Описываются различные аспекты работы с параметрами, включая типы и порядок их передачи, а также синтаксис вызова подпрограмм. Также упоминается возможность перегрузки процедур и рекурсивных вызовов, что повышает гибкость проектирования в VHDL.

![Куланов В.А.

[v.kulanov@csn.khai.edu]

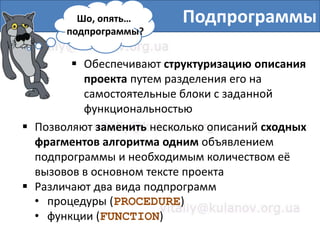

Подпрограммы.

Процедуры в языке VHDL

«Технологии проектирования

компьютерных систем»](https://image.slidesharecdn.com/lecturevhdlprocedures-170514200111/85/Subprograms-in-VHDL-Procedures-in-VHDL-1-320.jpg)

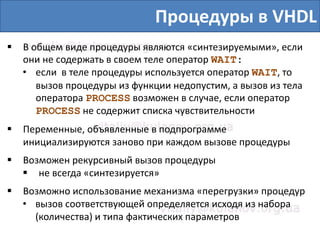

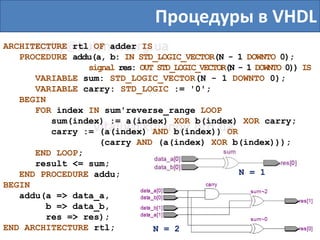

![Процедуры в VHDL

PROCEDURE name[(parameter_interface_list)] IS

{subprogram_declarative_item}

BEGIN

{sequential_statement}

END [PROCEDURE] [name];

SIGNAL, TYPE, FILE,

SUBTYPE, PROCEDURE,

FUNCTION, VARIABLE,

COMPONENT, CONSTANT

...-- последовательные операторы

a := 5

FOR … LOOP … END LOOP;

...

IF … THEN … ELSE … END IF;

Имя процедуры

Список формальных параметров

(может отсутствовать)](https://image.slidesharecdn.com/lecturevhdlprocedures-170514200111/85/Subprograms-in-VHDL-Procedures-in-VHDL-3-320.jpg)

![Список параметров процедуры

PROCEDURE name[(parameter_interface_list)] IS

...

([CONSTANT|VARIABLE|SIGNAL] identifier {,…}:

[IN|OUT|INOUT] type_indication [:= expression] {;…})

Имя/Идентификатор

параметра

Класс параметра

(может быть еще FILE)

Вид

параметра

Тип

параметра

Значение по умолчанию.

Может быть задано только

для параметров класса

CONSTANT и VARIABLE

PROCEDURE foo(val: INTEGER) -- val - CONSTANT

PROCEDURE foo(val: IN INTEGER) -- val - CONSTANT

PROCEDURE foo(val, bar: OUT INTEGER) -- val, bar - VARIABLE

PROCEDURE foo(val: INOUT INTEGER) -- val – VARIABLE](https://image.slidesharecdn.com/lecturevhdlprocedures-170514200111/85/Subprograms-in-VHDL-Procedures-in-VHDL-5-320.jpg)

![Вызов процедуры в VHDL

Вызов процедуры записывается в исходном коде как

отдельный оператор, который имеет следующий синтаксис:

[label:] name [(parameter_list)];

Метка Список фактических параметров

([parameter_name =>]

expression|signal_name|variable_name|OPEN, {…})

Формальный параметр

Два типа сопоставления:

Именованное (=>)

Позиционное

Фактический параметр

Выражение/Константное значение

Сигнал

Переменная

Ключевое слово OPEN - не используется или значение по умолчанию](https://image.slidesharecdn.com/lecturevhdlprocedures-170514200111/85/Subprograms-in-VHDL-Procedures-in-VHDL-6-320.jpg)

![Процедуры в VHDL

В теле процедуры может использоваться оператор

RETURN, назначение которого – завершение выполнения

процедуры:

[label:] RETURN;

PROCEDURE sort2(VARIABLE x1,x2: INOUT INTEGER) IS

VARIABLE t: INTEGER;

BEGIN

IF x1 > x2 THEN

RETURN;

ELSE

t := x1;

x1 := x2;

x2 := t;

END IF;

END PROCEDURE;

Как это сделать без

дополнительной

переменной "t"?](https://image.slidesharecdn.com/lecturevhdlprocedures-170514200111/85/Subprograms-in-VHDL-Procedures-in-VHDL-15-320.jpg)