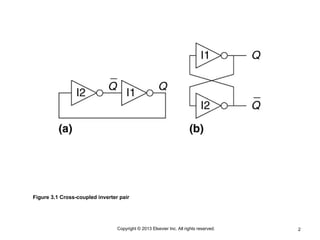

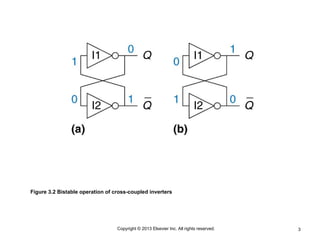

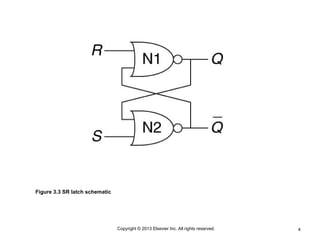

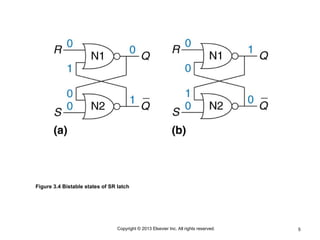

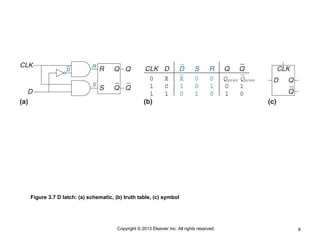

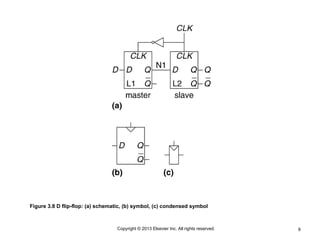

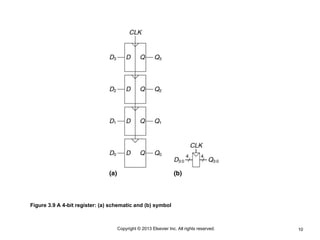

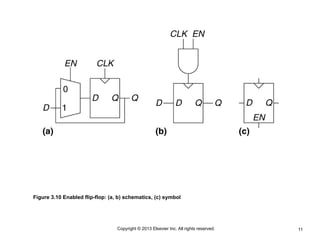

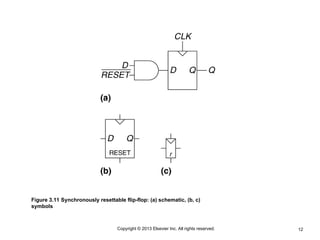

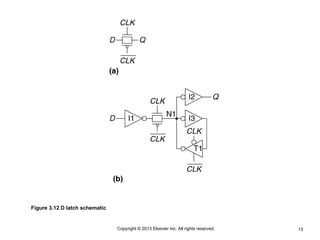

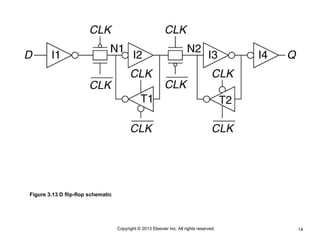

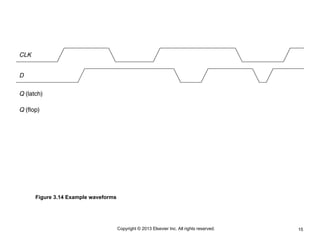

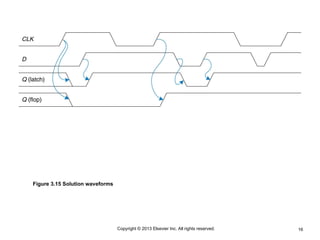

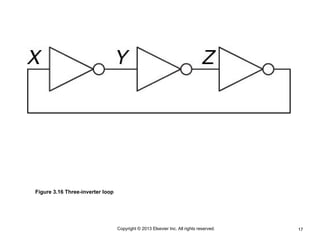

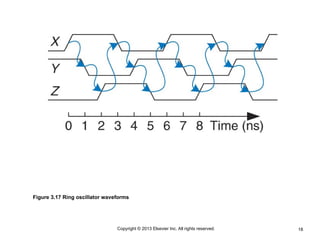

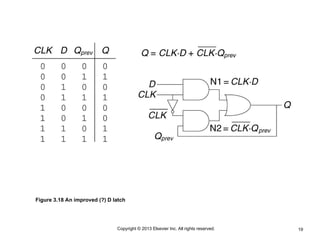

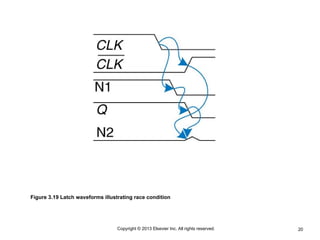

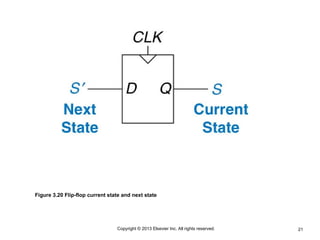

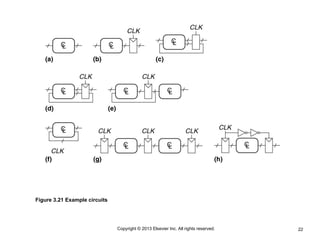

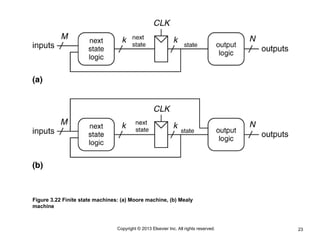

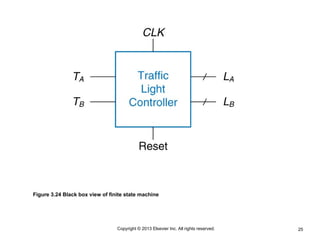

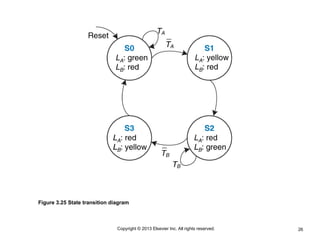

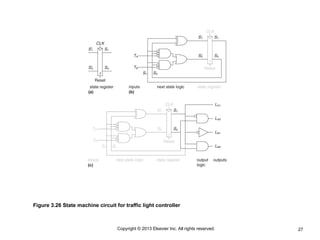

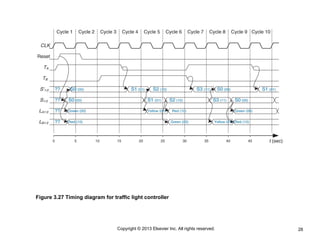

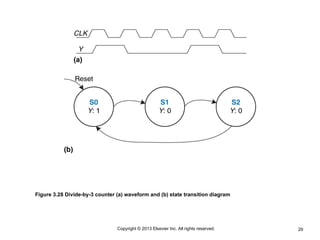

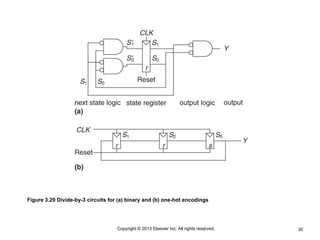

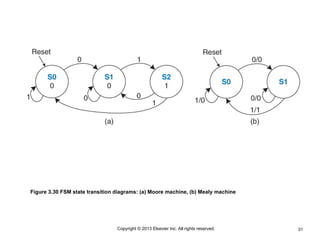

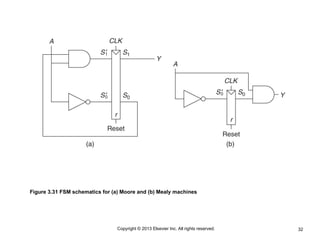

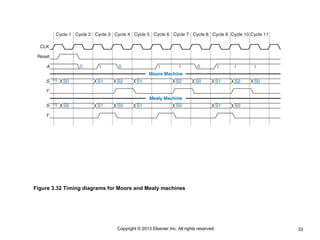

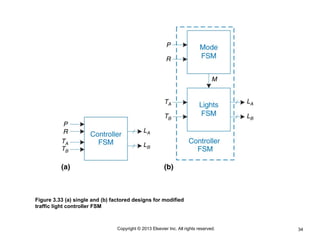

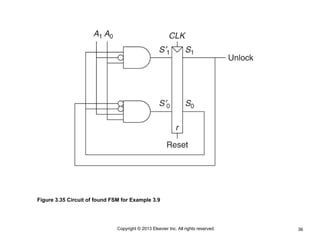

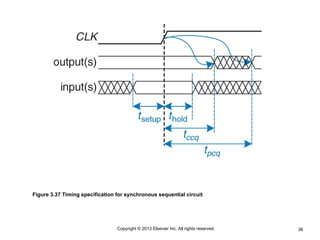

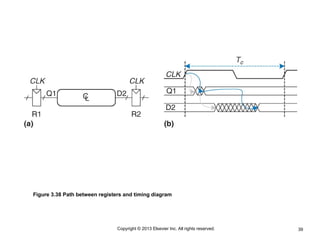

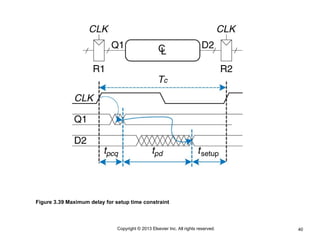

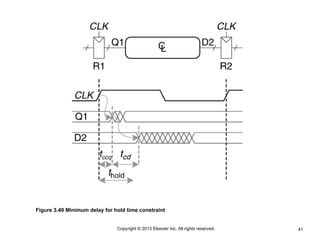

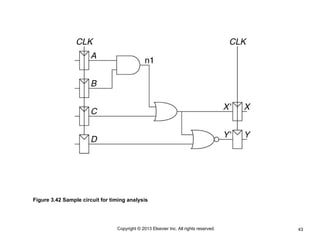

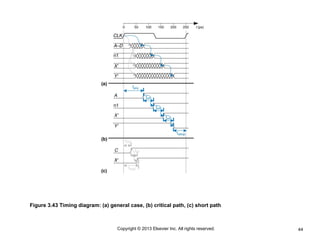

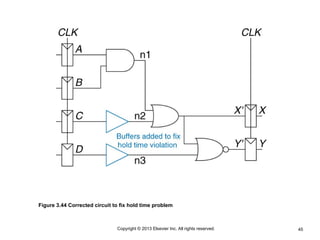

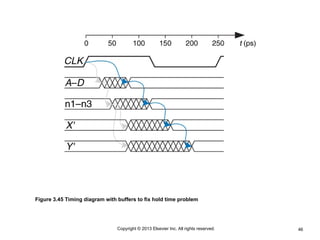

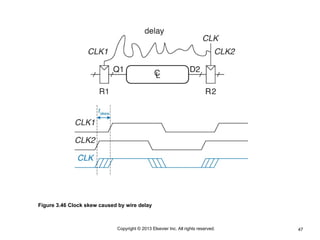

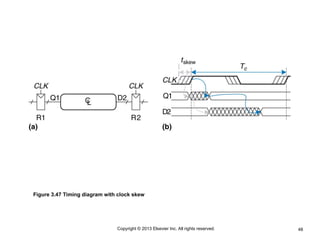

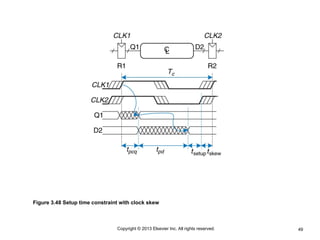

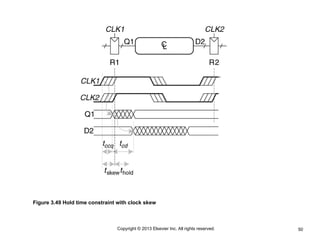

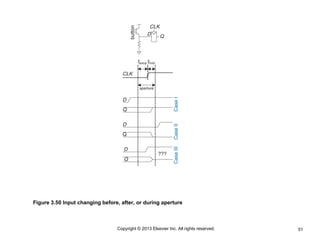

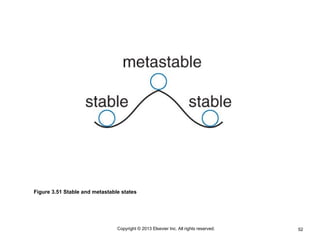

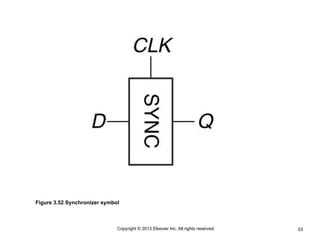

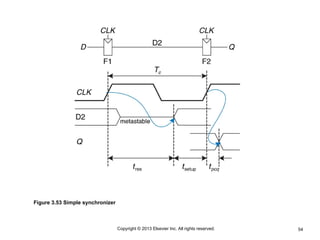

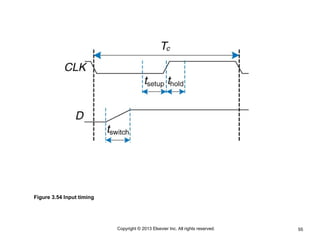

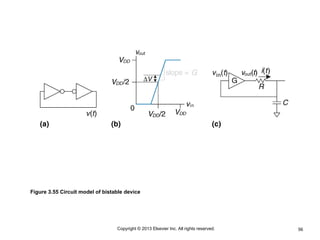

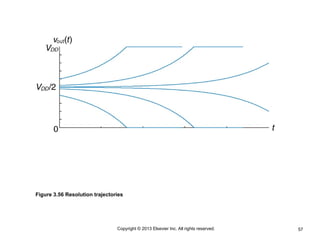

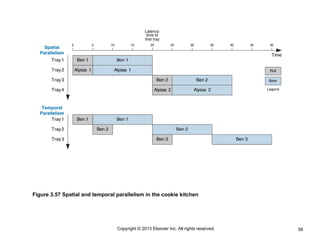

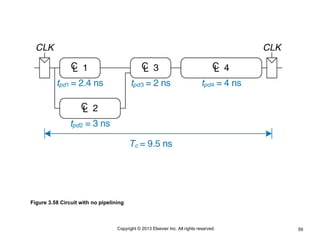

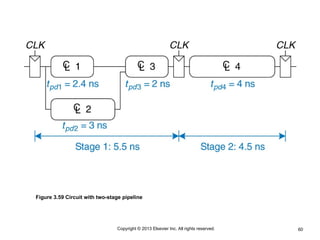

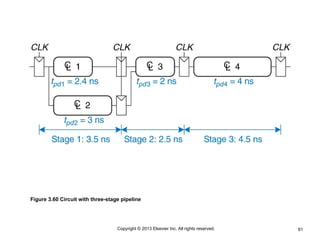

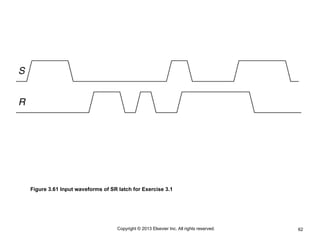

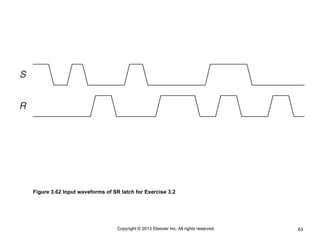

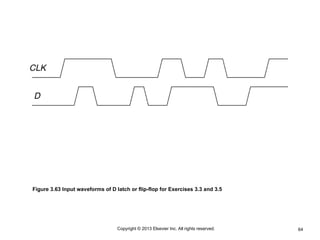

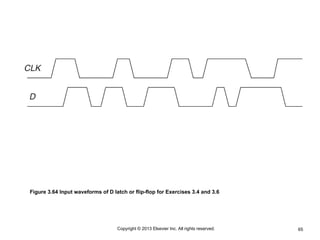

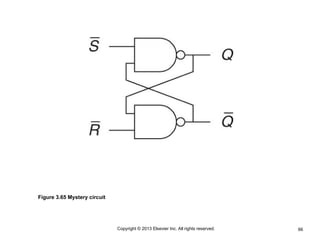

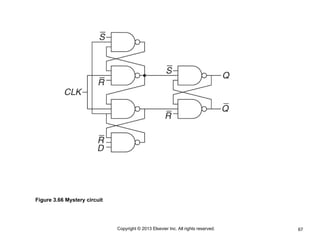

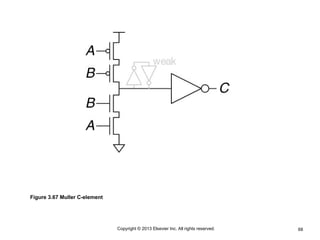

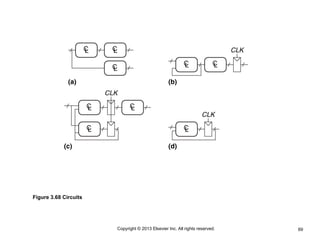

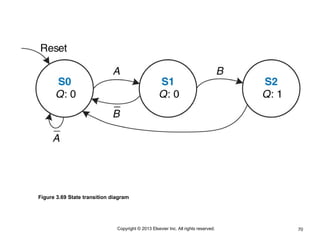

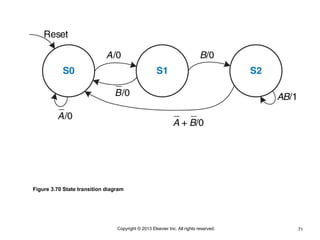

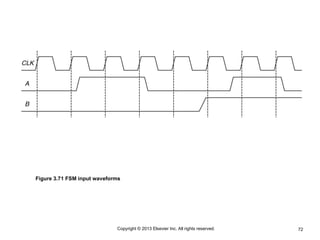

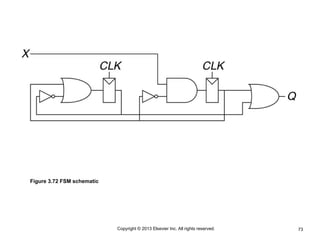

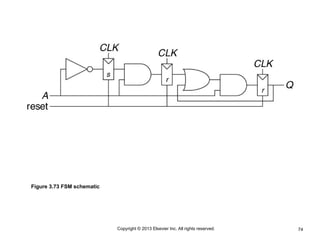

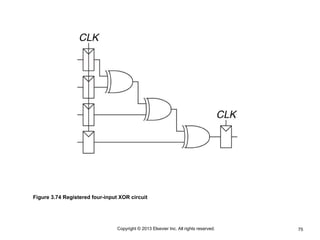

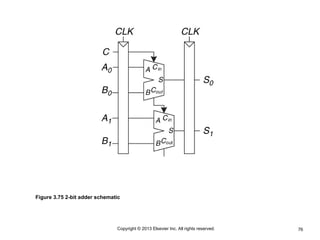

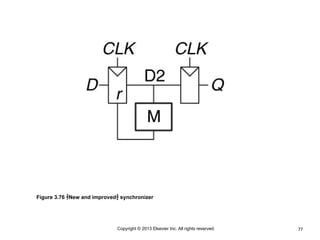

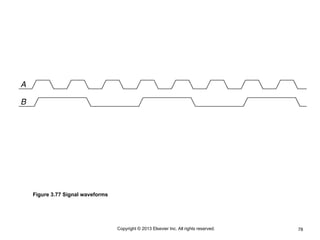

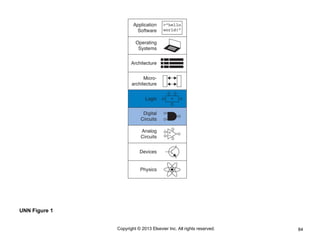

The document provides a detailed overview of sequential logic design, including various components such as SR and D latches and flip-flops, represented through schematics, truth tables, and timing diagrams. It illustrates the operation of finite state machines (FSM) including Moore and Mealy machines, along with practical examples like traffic light controllers and counters. Additionally, concepts like timing constraints, metastability, and circuit pipelining are discussed with accompanying figures and diagrams.