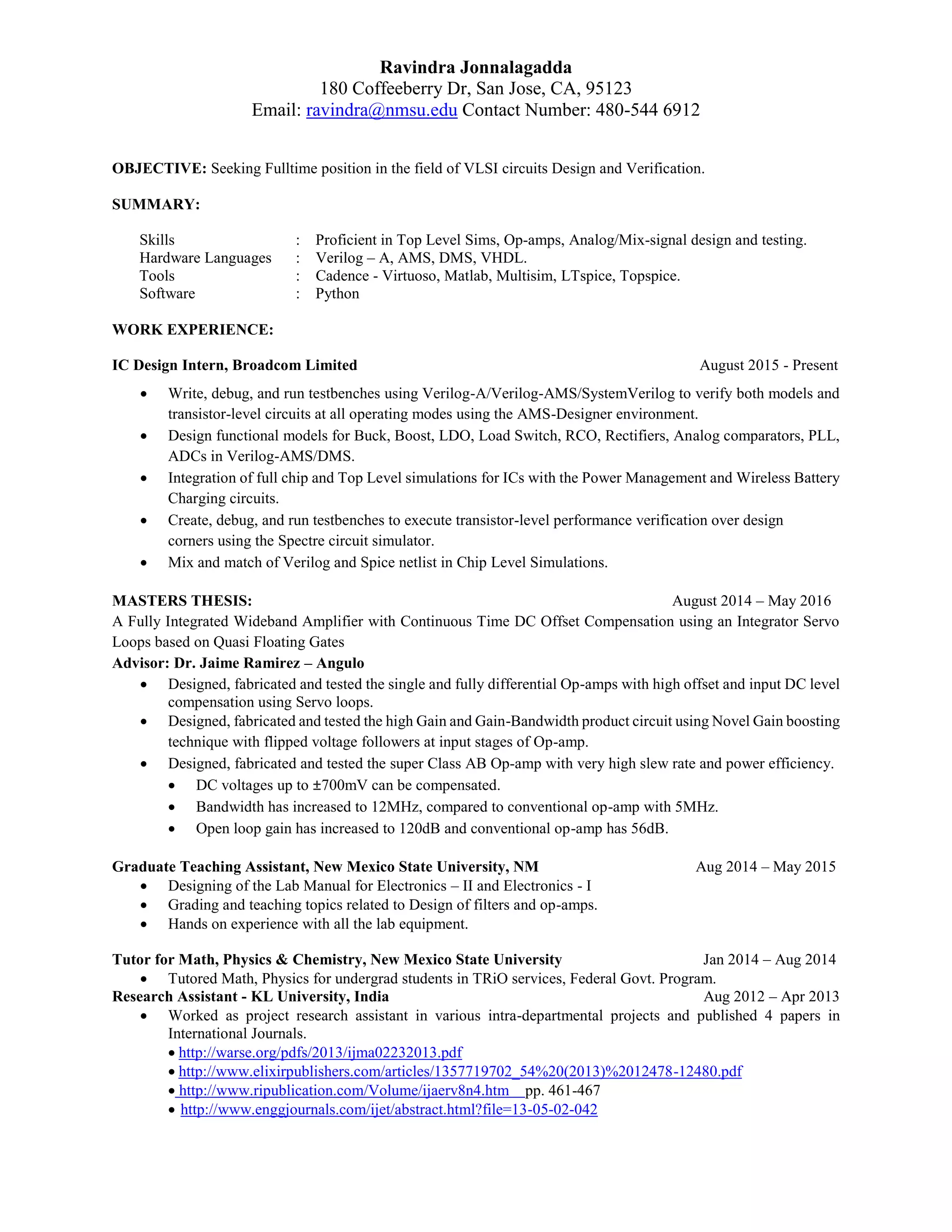

Ravindra Jonnalagadda is seeking a position in VLSI circuits design and verification with skills in analog/mixed-signal design, Verilog, VHDL, and CAD tools. He has work experience as an IC design intern at Broadcom where he designed models and verified circuits. He holds an M.S. in electrical engineering from New Mexico State University where he specialized in VLSI and completed projects in circuit design and digital systems.