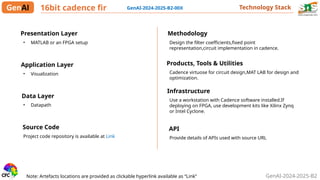

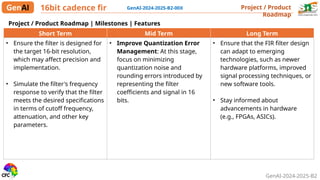

The document outlines a project for designing a 16-bit FIR filter using Cadence tools, aiming for real-time processing in ASIC/FPGA deployment. It details the design process from specifications to optimization, emphasizing hardware efficiency, digital signal processing, and various filter types. The project leverages advanced methodologies and tools for accurate frequency response and improved performance while addressing challenges like quantization error management.