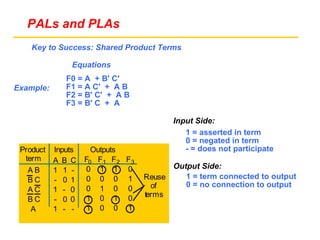

This document summarizes programmable logic devices including PALs and PLAs. It describes how PALs and PLAs can be personalized by making or breaking connections between pre-fabricated AND and OR gates. An example is provided to illustrate how a PAL or PLA can be programmed to implement different logic functions by selectively connecting product terms to outputs. The key differences between PALs and PLAs are also outlined.