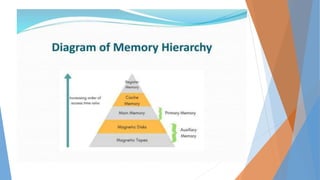

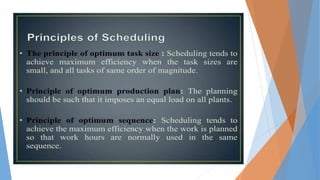

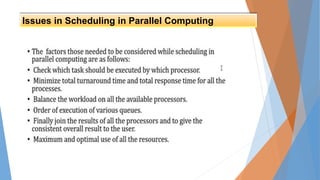

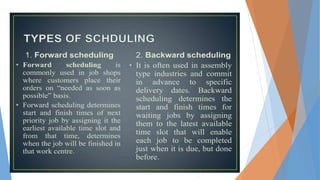

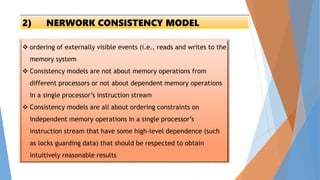

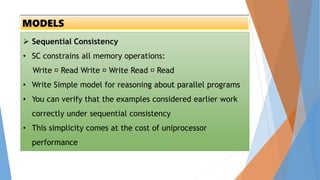

This document discusses key topics in parallel and distributed computing including scheduling, network consistency models, load balancing, and memory hierarchies. It describes issues in scheduling parallel tasks and different consistency models like sequential consistency. It also outlines types of load balancing and discusses memory hierarchies in parallel systems.

![Sequential consistency (SC) [Lamport]result of

execution is as if memory operations of each

process are executed in program

orderMEMORYP1 P3 P2 Pn](https://image.slidesharecdn.com/presentation-230107141405-ef763c8f/85/Parallel-and-distributed-Computing-9-320.jpg)